HS-3282

Pin Description (Continued)

PIN

31

32

33

34

SYMBOL

429D0

SECTION

Transmitter

Transmitter

Transmitter

Recs/Trans

DESCRIPTION

Data output from Transmitter

Data output from Transmitter.

429D0

ENTX

Transmitter Enable input signal to initiate data transmission from FIFO memory.

CWSTR

Control word input strobe signal to latch the control word from the databus into the control

word register.

35

36

37

-

-

-

No connection. Must be left open.

-

No connection. Must be left open or tied low but never tied high.

CLK

Recs/Trans

External clock input. May be either ten (10) or eighty (80) times the data rate. If using both

ARINC data rates it must be ten (10) times the highest data rate, (typically 1MHz).

38

39

TXCLK

MR

Transmitter

Recs/Trans

Transmitter Clock output. Delivers a clock frequency equal to the transmitter data rate.

Master Reset. Active low pulse used to reset FIFO, bit counters, gap timer, word count signal,

TX/R and various other flags and controls. Master reset does not reset the control word

register. Usually only used on Power-Up or System Reset.

40

-

-

No Connection.

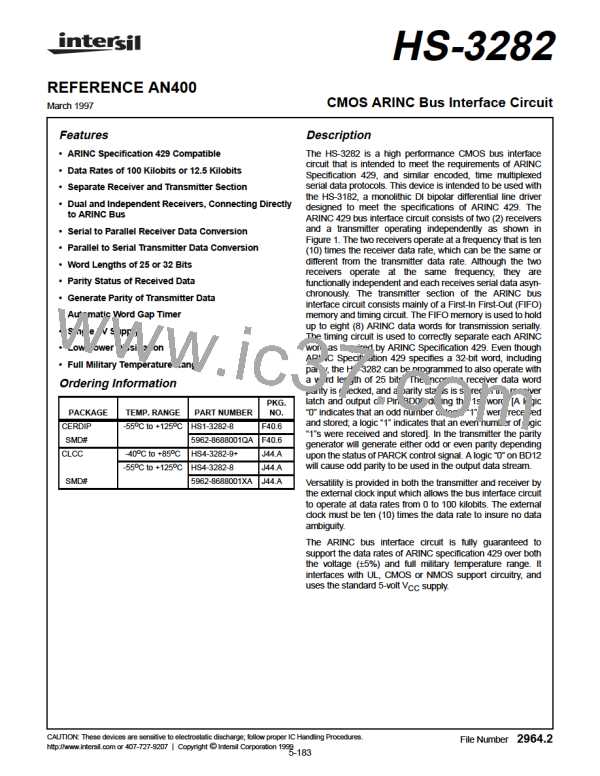

Pinout

20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

NC NC NC

5-186

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]