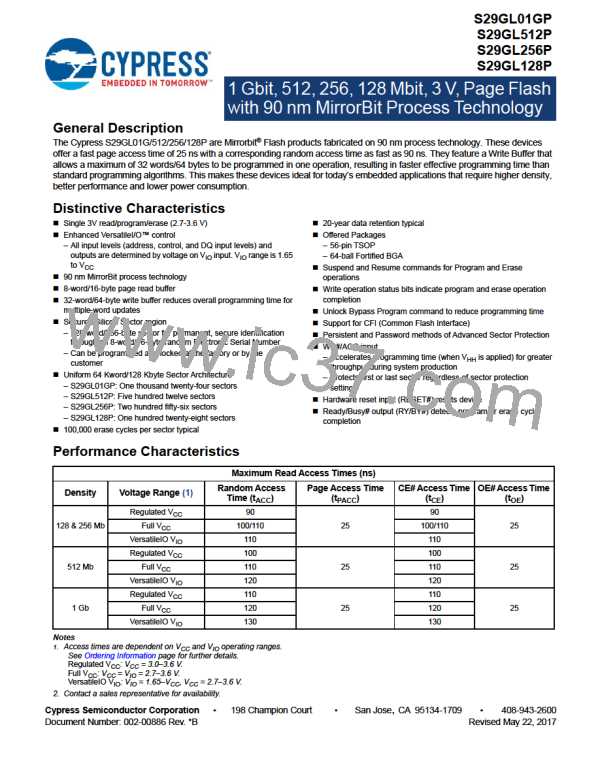

S29GL01GP

S29GL512P

S29GL256P

S29GL128P

11.7.3

S29GL-P Erase and Program Operations

S29GL-P Erase and Program Operations

Parameter

Speed Options

JEDEC

tAVAV

Std.

tWC

tAS

90

100

110

110

0

120 130 Unit

Description

Write Cycle Time (Note 1)

Address Setup Time

Min

Min

Min

Min

90

100

120 130 ns

tAVWL

ns

ns

ns

tASO Address Setup Time to OE# low during toggle bit polling

15

45

tWLAX

tAH

Address Hold Time

Address Hold Time From CE# or OE# high during toggle bit

polling

tAHT

Min

0

ns

tDVWH

tWHDX

tDS

tDH

Data Setup Time

Data Hold Time

Min

Min

Min

Min

Min

Min

Min

Min

Typ

30

0

ns

ns

ns

ns

ns

ns

ns

ns

µs

tCEPH CE# High during toggle bit polling

20

20

0

tOEPH Output Enable High during toggle bit polling

tELWL

tWHEH

tWLWH

tWHDL

tCS

tCH

tWP

CE# Setup Time

CE# Hold Time

Write Pulse Width

0

35

30

480

tWPH Write Pulse Width High

Write Buffer Program Operation (Notes 2, 3)

Effective Write Buffer Program Operation (Notes

2, 4)

Per Word Typ

Per Word Typ

15

µs

µs

tWHWH1 tWHWH1 Accelerated Effective Write Buffer Program

Operation (Notes 2, 4)

13.5

Program Operation (Note 2)

Accelerated Programming Operation (Note 2)

tWHWH2 tWHWH2 Sector Erase Operation (Note 2)

tVHH VHH Rise and Fall Time (Note 1)

tVCS VCC Setup Time (Note 1)

Word

Word

Typ

Typ

Typ

Min

Min

Max

Max

60

54

µs

µs

sec

ns

0.5

250

35

µs

ns

tBUSY Erase/Program Valid to RY/BY# Delay

90

tSEA

Sector Erase Timeout

50

µs

Notes

1. Not 100% tested.

2. See Section 11.6 for more information.

3. For 1–32 words/1–64 bytes programmed.

4. Effective write buffer specification is based upon a 32-word/64-byte write buffer operation.

5. Unless otherwise indicated, AC specifications for 110 ns speed option are tested with

VIO = VCC = 2.7 V. AC specifications for 110 ns speed options are tested with VIO = 1.8 V and VCC = 3.0 V.

Document Number: 002-00886 Rev. *B

Page 56 of 83

INFINEON [ Infineon ]

INFINEON [ Infineon ]