S29GL01GP

S29GL512P

S29GL256P

S29GL128P

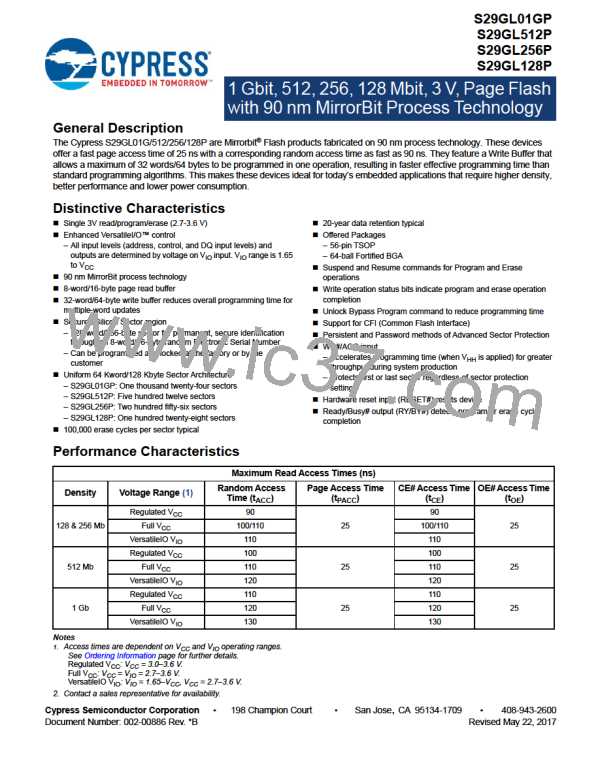

Power-up Sequence Timings

Parameter

Description

Speed

Unit

Reset Low Time from rising edge of VCC (or last Reset pulse) to

rising edge of RESET#

tVCS

Min

35

µs

Reset Low Time from rising edge of VIO (or last Reset pulse) to rising

edge of RESET#

tVIOS

tRH

Min

Min

35

µs

ns

Reset High Time before Read

200

Notes

1. VIO < VCC + 200 mV.

2. VIO and VCC ramp must be synchronized during power up.

3. If RESET# is not stable for tVCS or tVIOS

:

The device does not permit any read and write operations.

A valid read operation returns FFh.

A hardware reset is required.

4. VCC maximum power-up current (RST=VIL) is 20 mA.

Figure 11.8 Power-up Sequence Timings

V

CC

V

V

min

min

CC

V

IO

IO

tRH

CE#

tVIOS

tVCS

RESET#

Document Number: 002-00886 Rev. *B

Page 55 of 83

INFINEON [ Infineon ]

INFINEON [ Infineon ]