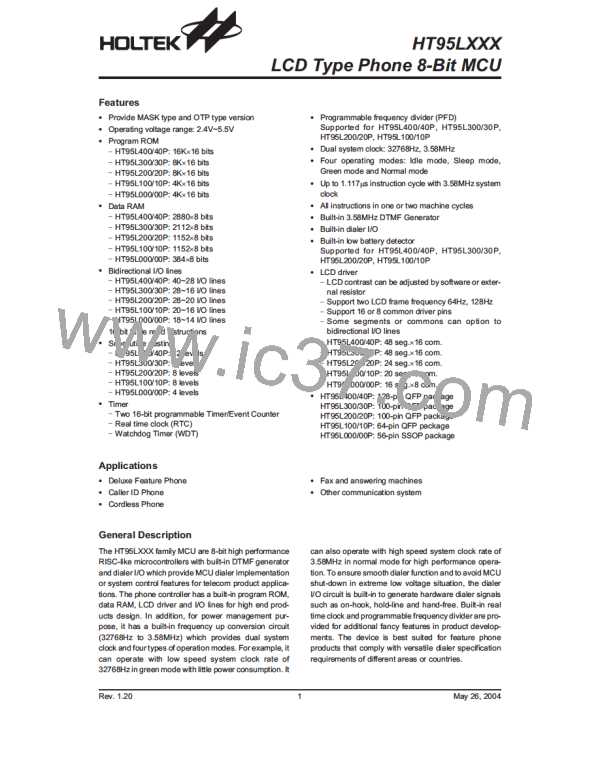

HT95LXXX

Register

Label

Bits

R/W

Function

4~0

RO

¾

Unused bit, read as ²0²

1: Enable frequency up conversion function to generate 3.58MHz

0: Disable frequency up conversion function to generate 3.58MHz

UPEN

MODE0

MODE1

5

6

7

RW

RW

RW

1: Disable 32768Hz oscillator while the HALT instruction is executed

MODE

(26H)

(Idle mode)

0: Enable 32768Hz oscillator while the HALT instruction is executed

(Sleep mode)

1: Select 3.58MHz as CPU system clock

0: Select 32768Hz as CPU system clock

Operation Mode Description

HALT

MODE1

Operation

Mode

System

MODE0

UPEN

32768Hz

3.58MHz

Instruction

Clock

3.58MHz

32768Hz

HALT

Not execute

Not execute

Be executed

Be executed

1

0

0

0

X

X

0

1

1

0

0

0

Normal

Green

Sleep

Idle

ON

ON

ON

OFF

OFF

OFF

ON

OFF

HALT

Note: ²X² means don¢t care

·

Sleep mode or Idle mode to Green mode:

resume to Green mode. In other words, a dummy period

is inserted after a wake-up. If the wake-up results from

an interrupt acknowledge signal, the actual interrupt

subroutine execution will be delayed by one or more cy-

cles. If the wake-up results in the next instruction execu-

tion, this will be executed immediately after the dummy

period is finished.

Method 1: Any reset condition occurred

Method 2: Any interrupt is active

Method 3: Port A wake-up

Note:The Timer 0, Timer 1, RTC and dialer I/O inter-

rupt function will not work at the Idle mode be-

cause the 32768Hz crystal is stopped.

The reset conditions include power on reset, external re-

set, WDT time-out reset. By examining the processor

status flag, PDF and TO, the program can distinguish

between different ²reset conditions². Refer to the Reset

function for detailed description.

To minimize power consumption, all the I/O pins should

be carefully managed before entering the Sleep mode

or Idle mode.

The Sleep mode or Idle mode is initialized by the HALT

instruction and results in the following.

The port A wake-up and interrupt can be considered as

a continuation of normal execution. Each bit in port A

can be independently selected to wake-up the device by

mask option. Awakening from Port A stimulus, the pro-

gram will resume execution of the next instruction.

·

·

The system clock will be turned off.

The WDT function will be disabled if the WDT clock

source is the instruction clock.

·

·

·

The WDT function will be disabled if the WDT clock

source is the 32768Hz in Idle mode.

Any valid interrupts from Sleep mode or Idle mode may

cause two sequences. One is if the related interrupt is

disabled or the interrupt is enabled but the stack is full,

the program will resume execution at the next instruc-

tion. The other is if the interrupt is enabled and the stack

is not full, the regular interrupt response takes place. It is

necessary to mention that if an interrupt request flag is

set to ²1² before entering the Sleep mode or Idle mode,

the wake-up function of the related interrupt will be dis-

abled.

The WDT will still function if the WDT clock source is

the WDT OSC.

If the WDT function is still enabled, the WDT counter

and WDT prescaler will be cleared and recounted

again.

·

The contents of the on chip RAM and registers remain

unchanged.

·

·

All the I/O ports maintain their original status.

Once a Sleep mode or Idle mode wake-up event occurs,

it will take SST delay time (1024 system clock period) to

The flag PDF is set and the flag TO is cleared by hard-

ware.

Rev. 1.20

17

May 26, 2004

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]