áç

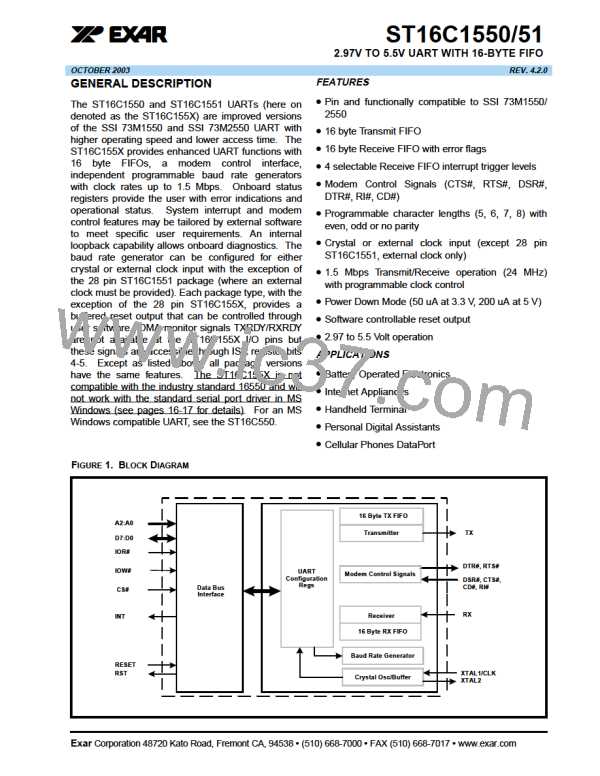

ST16C1550/51

2.97V TO 5.5V UART WITH 16-BYTE FIFO

REV. 4.2.0

IER[2]: Receive Line Status Interrupt Enable

If any of the LSR register bits 1, 2, 3 or 4 is a logic 1, it will generate an interrupt to inform the host controller

about the error status of the current data byte in FIFO. LSR bit-1 generates an interrupt immediately when the

character has been received. LSR bits 2-4 generate an interrupt when the character with errors is read out of

the FIFO.

• Logic 0 = Disable the receiver line status interrupt (default).

• Logic 1 = Enable the receiver line status interrupt.

IER[3]: Modem Status Interrupt Enable

• Logic 0 = Disable the modem status register interrupt (default).

• Logic 1 = Enable the modem status register interrupt.

IER[4]: Reserved

IER[5]: Special Mode Enable

• Logic 0 = Disable special mode functions (default).

• Logic 1 = Enable special mode functions in addition to basic ST16C1450 functions. Enables ISR bits 4-5

(TXRDY/RXRDY), MCR bit-2 (soft reset) and MCR bit-7 (power down) functions.

IER[7:6]: Reserved

4.4

Interrupt Status Register (ISR) - Read-Only

The UART provides multiple levels of prioritized interrupts to minimize external software interaction. The

Interrupt Status Register (ISR) provides the user with six interrupt status bits. Performing a read cycle on the

ISR will give the user the current highest pending interrupt level to be serviced, others are queued up to be

serviced next. No other interrupts are acknowledged until the pending interrupt is serviced. The Interrupt

Source Table, Table 5, shows the data values (bits 0-3) for the interrupt priority levels and the interrupt sources

associated with each of these interrupt levels.

4.4.1

Interrupt Generation:

• LSR is by any of the LSR bits 1, 2, 3 and 4.

• RXRDY is by RX trigger level.

• RXRDY Time-out is by a 4-char plus 12 bits delay timer.

• TXRDY is by TX trigger level or TX FIFO empty.

• MSR is by any of the MSR bits 0, 1, 2 and 3.

4.4.2

Interrupt Clearing:

• LSR interrupt is cleared by a read to the LSR register (but flags and tags not cleared until character(s) that

generated the interrupt(s) has been emptied or cleared from FIFO).

• RXRDY interrupt is cleared by reading data until FIFO falls below the trigger level.

• RXRDY Time-out interrupt is cleared by reading RHR until empty.

• TXRDY interrupt is cleared by a read to the ISR register AND disabling the TXRDY interrupt (set IER bit-1 =

0), or by loading data into the TX FIFO.

• MSR interrupt is cleared by a read to the MSR register.

17

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]