áç

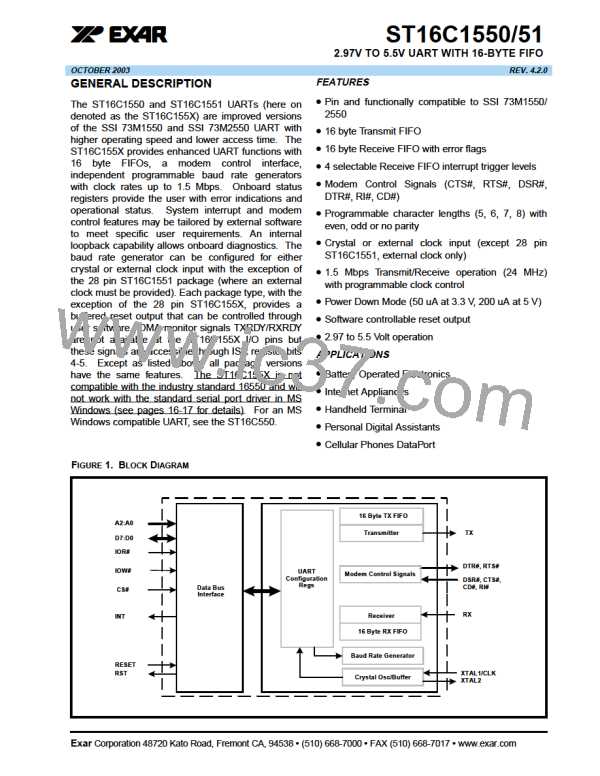

ST16C1550/51

2.97V TO 5.5V UART WITH 16-BYTE FIFO

REV. 4.2.0

.

TABLE 4: INTERNAL REGISTERS DESCRIPTION. SHADED BITS ARE ENABLED WHEN EFR BIT-4=1

ADDRESS

REG

READ/

WRITE

BIT-7

BIT-6

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

COMMENT

A2-A0

NAME

16C550 Compatible Registers

0 0 0

0 0 0

0 0 1

RHR

THR

RD

Bit-7

Bit-7

0

Bit-6

Bit-6

0

Bit-5

Bit-5

Bit-4

Bit-4

0

Bit-3

Bit-3

Bit-2

Bit-2

Bit-1

Bit-1

TX

Bit-0

Bit-0

WR

IER RD/WR

Special

Mode

Enable

Modem RXLine

Status

RX

Data

Int.

Status Empty

Int. Int.

Enable Enable Enable

Int.

Enable

(Enable

ISR bits

5-4, FCR

bits 5-4,

MCR bits

7, 2)

LCR[7] = 0

0 1 0

0 1 0

ISR

RD

FIFOs

Enabled Enabled

FIFOs

0/

0/

INT

INT

INT

INT

Source Source Source Source

Bit-3

RXRDY TXRDY

0/ 0/

Bit-2

Bit-1

Bit-0

FCR

WR RXFIFO RXFIFO

Trigger Trigger

DMA

Mode

Enable

TX

FIFO

Reset Reset

RX

FIFOs

FIFO Enable

TXFIFO TXFIFO

Trigger Trigger

(MSB)

(LSB)

(MSB)

(LSB)

0 1 1

1 0 0

LCR RD/WR Divisor Set TX

Set

Even

Parity

Parity

Enable

Stop

Bits

Word

Length Length

Bit-1 Bit-0

Word

Enable

Break

Parity

MCR RD/WR

0/

0

0

Internal (OP2#)/ (OP1#)/ RTS# DTR#

Loop-

back

Enable

INT

Output Output

Control Control

Power

Down

Mode

SOFT

Reset

Output

Enable

1 0 1

LSR

RD

RD

RXFIFO THR &

THR

Empty

RX

Break

RX

RX

Parity

Error

RX

Over-

run

RX

Data

Ready

Global

Error

TSR

Empty

LCR[7] = 0

Framing

Error

Error

1 1 0

1 1 1

MSR

CD#

RI#

DSR#

Input

CTS#

Input

Delta

CD#

Delta

RI#

Delta

DSR# CTS#

Delta

Input

Input

SPR RD/WR

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

Baud Rate Generator Divisor

0 0 0

0 0 1

DLL RD/WR

DLM RD/WR

Bit-7

Bit-7

Bit-6

Bit-6

Bit-5

Bit-5

Bit-4

Bit-4

Bit-3

Bit-3

Bit-2

Bit-2

Bit-1

Bit-1

Bit-0

Bit-0

LCR[7] = 1

15

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]