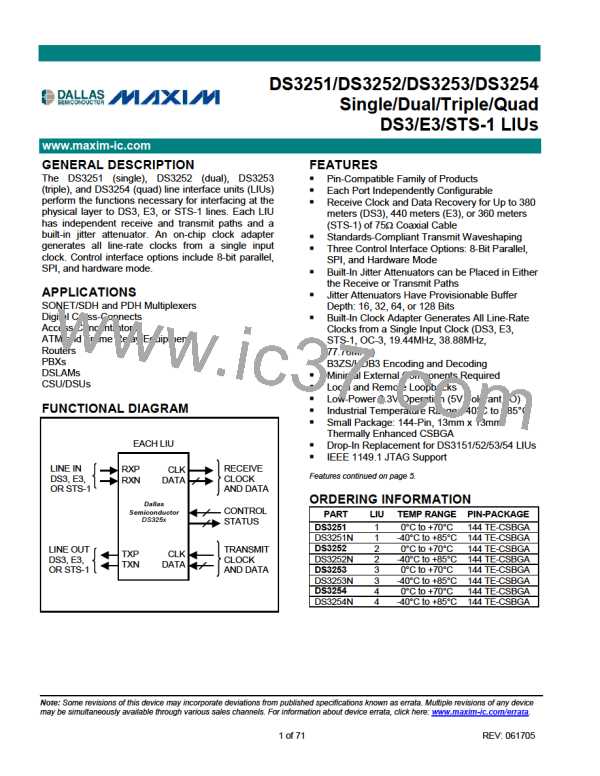

DS3251/DS3252/DS3253/DS3254

7. REGISTER DESCRIPTIONS

When the DS325x is configured in either of the two CPU bus modes (HW = 0), the registers shown in Table 7-A

are accessible through the CPU bus interfaces. All registers for the LIU ports are forced to their default values

during an internal power-on reset or when the RST pin is driven low. Setting an LIU’s RST bit high forces all

registers for that LIU to their default values. All register bits marked “—” must be written 0 and ignored when read.

The TEST registers must be left at their reset value of 00h for normal operation.

On the DS3253, only registers for LIUs 1, 2, and 3 are available. Writes into LIU 4 address space are ignored.

Reads from LIU 4 address space return all zeros. On the DS3252, address line A5 is not present, limiting the

address space to the LIU 1 and LIU 2 registers. On the DS3251, address lines A5 and A4 are not present, limiting

the address space to the LIU 1 registers.

Table 7-A. Register Map

ADDRESS

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

LIU 1

00h

01h

GCR1

TCR1

E3M

JAL[1]

ITU

STS

TBIN

RBIN

—

JAEL

JAEIE

RCV[6]

RCV[14]

E3MOE

—

LLB

RLB

TJA

RJA

TDSA

TPD

TDSB

TTS

—

RST

TCINV

RCINV

TDM

TLBO

JAL[0]

02h

RCR1

RPD

RTS

RMON

RLOL

RCVUD

RLOS

03h

SR1

—

PRBS

PRBSL

PRBSIE

RCV[4]

RCV[12]

—

—

—

04h

SRL1

JAFL

JAFIE

RCV[7]

RCV[15]

T3MOE

—

TDML

TDMIE

RCV[5]

RCV[13]

STMOE

—

PBERL

PBERIE

RCV[3]

RCV[11]

—

RCVL

RCVIE

RCV[2]

RCV[10]

RLOLL

RLOLIE

RCV[1]

RCV[9]

RLOSL

RLOSIE

RCV[0]

RCV[8]

05h

SRIE1

06h

RCVL1

RCVH1

CACR

07h

08h

AMCSEL[1] AMCSEL[0] AMCEN

09h–0Fh

Test Registers

—

—

—

—

—

LIU 2

LLB

TCINV

RCINV

TDM

10h

11h

GCR2

TCR2

E3M

JAL[1]

ITU

STS

TBIN

RBIN

—

RLB

TJA

RJA

TDSA

TPD

TDSB

TTS

—

RST

JAL[0]

RCVUD

RLOS

RLOSL

RLOSIE

RCV[0]

RCV[8]

—

TLBO

RMON

RLOL

RLOLL

RLOLIE

RCV[1]

RCV[9]

—

12h

RCR2

RPD

RTS

13h

SR2

—

PRBS

PRBSL

PRBSIE

RCV[4]

RCV[12]

—

—

—

14h

SRL2

JAFL

JAFIE

RCV[7]

RCV[15]

—

JAEL

JAEIE

RCV[6]

RCV[14]

—

TDML

TDMIE

RCV[5]

RCV[13]

—

PBERL

PBERIE

RCV[3]

RCV[11]

—

RCVL

RCVIE

RCV[2]

RCV[10]

—

15h

SRIE2

16h

RCVL2

RCVH2

unused

Test Registers

17h

18h

19h–1Fh

—

—

—

—

—

—

—

—

LIU 3

LLB

20h

21h

GCR3

TCR3

E3M

JAL[1]

ITU

STS

TBIN

RBIN

—

RLB

TJA

RJA

TDSA

TPD

TDSB

TTS

—

RST

JAL[0]

RCVUD

RLOS

RLOSL

RLOSIE

RCV[0]

RCV[8]

—

TCINV

RCINV

TDM

TLBO

RMON

RLOL

RLOLL

RLOLIE

RCV[1]

RCV[9]

—

22h

RCR3

RPD

RTS

23h

SR3

—

PRBS

PRBSL

PRBSIE

RCV[4]

RCV[12]

—

—

—

24h

SRL3

JAFL

JAFIE

RCV[7]

RCV[15]

—

JAEL

JAEIE

RCV[6]

RCV[14]

—

TDML

TDMIE

RCV[5]

RCV[13]

—

PBERL

PBERIE

RCV[3]

RCV[11]

—

RCVL

RCVIE

RCV[2]

RCV[10]

—

25h

SRIE3

26h

RCVL3

RCVH3

unused

Test Registers

27h

28h

29h–2Fh

—

—

—

—

—

—

—

—

LIU 4

LLB

30h

31h

GCR4

TCR4

E3M

JAL[1]

ITU

STS

TBIN

RBIN

—

RLB

TJA

RJA

TDSA

TPD

TDSB

TTS

—

RST

JAL[0]

RCVUD

RLOS

RLOSL

RLOSIE

RCV[0]

RCV[8]

—

TCINV

RCINV

TDM

TLBO

RMON

RLOL

RLOLL

RLOLIE

RCV[1]

RCV[9]

—

32h

RCR4

RPD

RTS

33h

SR4

—

PRBS

PRBSL

PRBSIE

RCV[4]

RCV[12]

—

—

—

34h

SRL4

JAFL

JAFIE

RCV[7]

RCV[15]

—

JAEL

JAEIE

RCV[6]

RCV[14]

—

TDML

TDMIE

RCV[5]

RCV[13]

—

PBERL

PBERIE

RCV[3]

RCV[11]

—

RCVL

RCVIE

RCV[2]

RCV[10]

—

35h

SRIE4

36h

RCVL4

RCVH4

unused

Test Registers

37h

38h

39h–3Fh

—

—

—

—

—

—

—

—

Note 1: Underlined bits are read-only; all other bits are read-write.

Note 2: The registers are named REGn, where n = the LIU number (1, 2, 3, or 4). The register names are hyperlinks to the register descriptions.

Note 3: The bit names are the same for each LIU register set.

15 of 71

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]