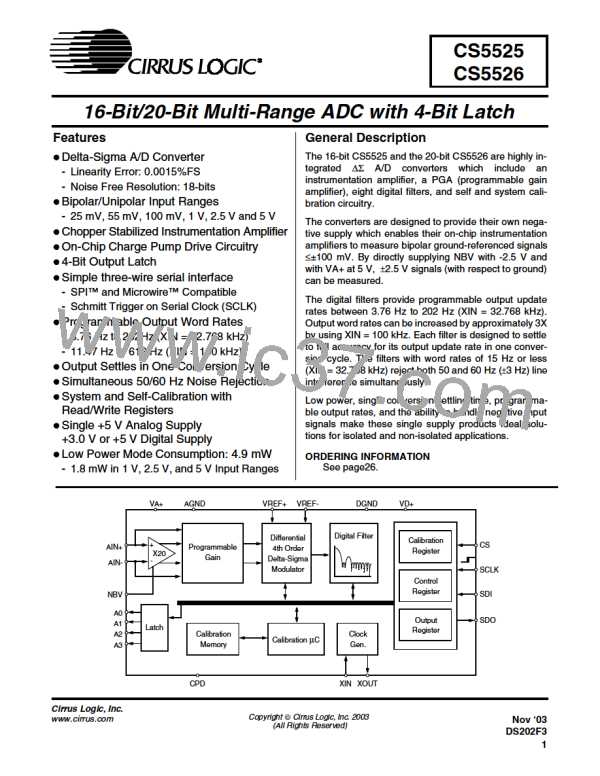

CS5525 CS5526

Configuration Register

D23(MSB)

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

A3

A2

A1

A0

NU

CFS

NU

LPM

WR2

WR1

WR0

U/B

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

G2

G1

G0

PD

RS

RV

PF

PSS

DF

CC2

CC1

CC0

BIT

NAME

VALUE

FUNCTION

D23-D20 Latch Outputs, A3-A0

0000

0

R* Latch Output Pins A3-A0 mimic the D23-D20 Register bits.

D19

D18

Not Used, NU

R

R

Must always be logic 0.

Chop Frequency Select,

CFS

0

1

256 Hz Amplifier chop frequency

32768 Hz Amplifier chop frequency

D17

D16

Not Used, NU

0

R

R

Must always be logic 0.

Low Power Mode, LPM

0

1

Normal Mode

Reduced Power mode

D15-D13 Word Rate, WR2-0

Note: For

000

001

010

011

100

101

110

111

R

15.0 Hz (2182 XIN cycles)

30.1 Hz (1090 XIN cycles)

60.0 Hz (546 XIN cycles)

123.2 Hz (266 XIN cycles)

168.9 Hz (194 XIN cycles)

202.3 Hz (162 XIN cycles)

3.76 Hz (8722 XIN cycles)

7.51 Hz (4362 XIN cycles)

XIN = 32.768kHz

D12

Unipolar/Bipolar, U/B

Gain Bits, G2-G0

0

1

R

R

Bipolar Measurement mode

Unipolar Measurement mode

D11-D9

000

001

010

100 mV (assumes VREF = 2.5V)

55 mV

25 mV

1 V

011

100

5.0 V

101

2.5 V

110/111

Not Used.

D8

Pump Disable, PD

Reset System, RS

Reset Valid , RV

Port Flag, PF

0

1

R

R

Charge Pump Enabled

For PD = 1, the CPD pin goes to a Hi-Z output state.

D7

0

1

Normal Operation

Activate a Reset cycle. To return to Normal Operation write bit to zero.

D6

0

1

No reset has occurred or bit has been cleared (read only).

Valid Reset has occurred. (Cleared when read.)

R

R

D5

0

1

Port Flag mode inactive

Port Flag mode active

D4

Power Save Select, PSS

Done Flag, DF

0

1

R

R

R

Standby Mode (Oscillator active, allows quick power-up)

Sleep Mode (Oscillator inactive)

D3

0

1

Done Flag bit is cleared (read only).

Calibration or Conversion cycle completed (read only).

D2-D0

Calibration Control Bits,

CC2-CC0

000

001

010

011

100

101

110

111

Normal Operation (no calibration)

Offset -- Self-Calibration

Gain -- Self-Calibration

Offset Self-Calibration followed by Gain Self-Calibration

Not used.

Offset -- System Calibration

Gain -- System Calibration

Not Used.

* R indicates the bit value after the part is reset

Table 2. Configuration Register

12

DS202F3

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]