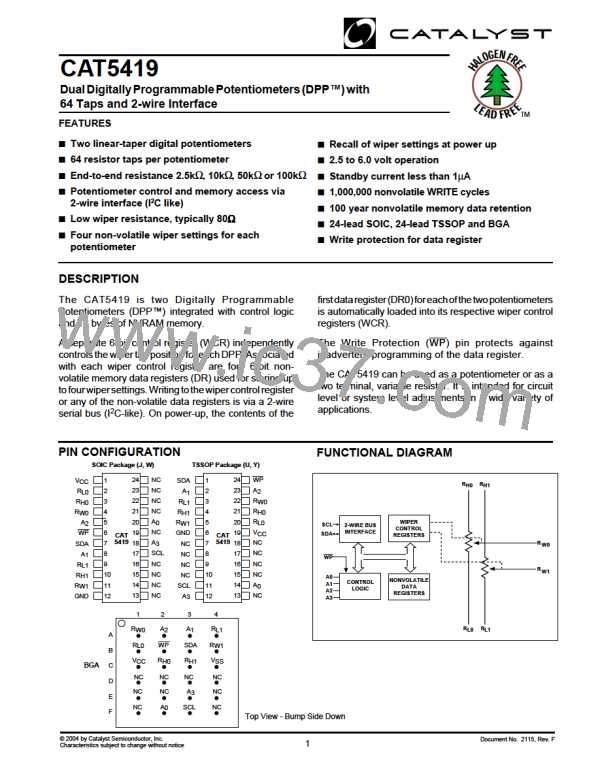

CAT5419

SERIAL BUS PROTOCOL

theparticularslavedeviceitisrequesting. Thefourmost

significant bits of the 8-bit slave address are fixed as

0101 for the CAT5419 (see Figure 5). The next four

significant bits (A3, A2, A1, A0) are the device address

bitsanddefinewhichdevicetheMasterisaccessing. Up

to sixteen devices may be individually addressed by the

system. Typically, +5V and ground are hard-wired to

these pins to establish the device's address.

The following defines the features of the 2-wire bus

protocol:

(1) Data transfer may be initiated only when the bus

is not busy.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any

changes in the data line while the clock is high will

be interpreted as a START or STOP condition.

After the Master sends a START condition and the slave

address byte, the CAT5419 monitors the bus and

responds with an acknowledge (on the SDA line) when

its address matches the transmitted slave address.

The device controlling the transfer is a master,

typically a processor or controller, and the device

being controlled is the slave. The master will always

initiate data transfers and provide the clock for both

transmit and receive operations. Therefore, the

CAT5419 will be considered a slave device in all

applications.

Acknowledge

Afterasuccessfuldatatransfer, eachreceivingdeviceis

required to generate an acknowledge. The

Acknowledging device pulls down the SDA line during

the ninth clock cycle, signaling that it received the 8 bits

of data.

START Condition

The START Condition precedes all commands to the

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT5419 monitors the

SDA and SCL lines and will not respond until this

condition is met.

The CAT5419 responds with an acknowledge after

receivingaSTARTconditionanditsslaveaddress. Ifthe

device has been selected along with a write operation,

it responds with an acknowledge after receiving each

8-bit byte.

STOP Condition

WhentheCAT5419isinaREADmodeittransmits8bits

of data, releases the SDA line, and monitors the line for

anacknowledge. Onceitreceivesthisacknowledge, the

CAT5419 will continue to transmit data. If no

acknowledgeissentbytheMaster,thedeviceterminates

data transmission and waits for a STOP condition.

A LOW to HIGH transition of SDA when SCL is HIGH

determinestheSTOPcondition.Alloperationsmustend

with a STOP condition.

DEVICE ADDRESSING

The bus Master begins a transmission by sending a

STARTcondition. TheMasterthensendstheaddressof

Figure 4. Acknowledge Timing

SCL FROM

MASTER

1

8

9

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

START

ACKNOWLEDGE

Document No. 2115, Rev. F

6

CATALYST [ CATALYST SEMICONDUCTOR ]

CATALYST [ CATALYST SEMICONDUCTOR ]