PCM1804

SLES022A – DECEMBER 2001

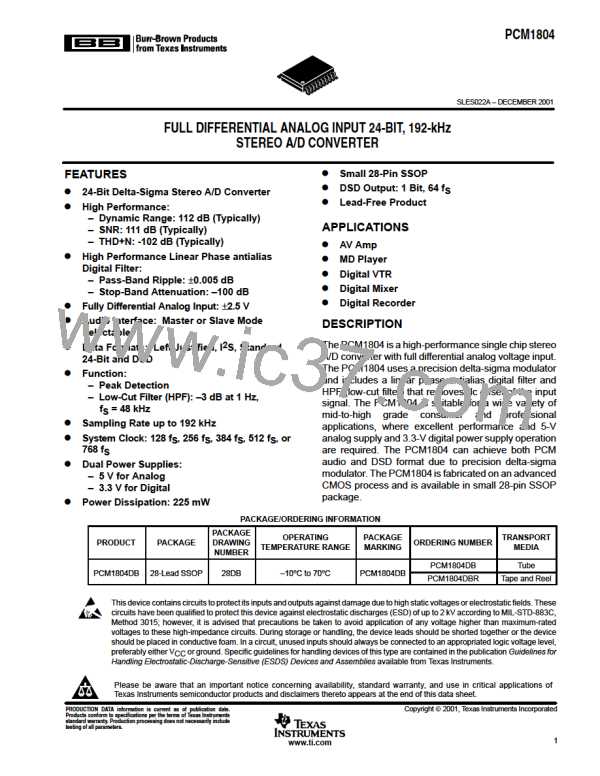

PRINCIPLES OF OPERATION

interface timing for PCM (continued)

t

(LRCP)

1.4 V

1.4 V

LRCK

t

t

(LRSU)

(LRHD)

t

t

w(BCKL)

w(BCKH)

BCK

DATA

t

(BCKP)

t

t

(LRDO)

(CKDO)

0.5 V

DD

PARAMETERS

MIN

TYP

MAX

UNIT

BCK period, t

1/(64 f ) 1/(64 f ) 1/(48 f )

(BCKP)

S

S

S

BCK pulse width high, t

32

ns

ns

ns

ns

w(BCKH)

BCK pulse width low, t

32

12

12

w(BCKL)

LRCK setup time to BCK rising edge, t

(LRSU)

LRCK hold time to BCK rising edge, t

LRCK period, t

(LRHD)

1/f

S

(LRCP)

Delay time BCK falling edge to DATA valid, t

5

5

25

25

10

10

ns

ns

ns

ns

(CKDO)

(LRDO)

Delay time LRCK edge to DATA valid, t

Rising time of all signals, t

r

Falling time of all signals, t

f

NOTES: A. Rising and falling time is measured from 10% to 90% of IN/OUT signals swing.

B. Load capacitance of DATA/DSDR signal is 10 pF.

Figure 38. Audio Data Interface Timing for PCM (Slave Mode: LRCK and BCK Work as Inputs)

interface timing for DSD

Figure 39 and Figure 40 illustrate the interface timing for DSD.

DSDBCK

DSDL

DSDR

D

D

D

D

D

D

D

D

D

D

D

D

D

D

n–3

n–3

n–2

n–2

n–1

n–1

n

n

n+1

n+1

n+2

n+2

n+3

n+3

Figure 39. Audio Data Format

23

www.ti.com

BB [ BURR-BROWN CORPORATION ]

BB [ BURR-BROWN CORPORATION ]