VRAM

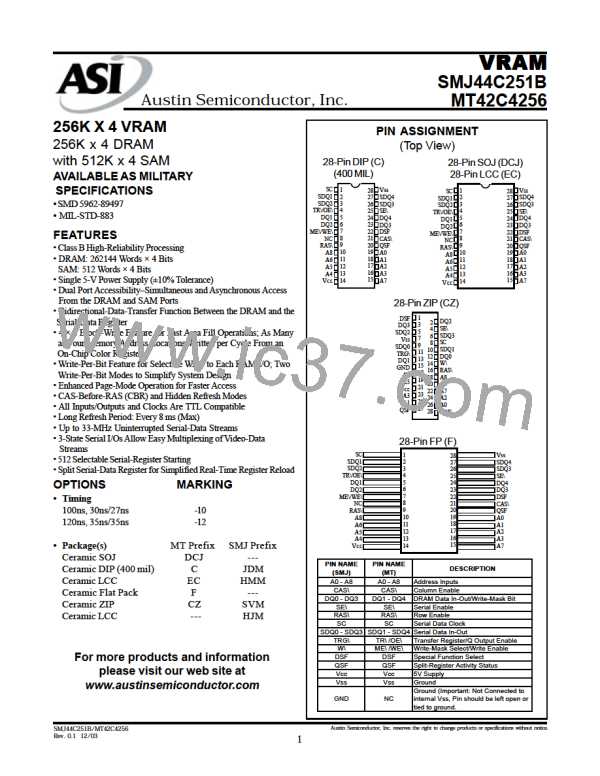

SMJ44C251B

MT42C4256

Austin Semiconductor, Inc.

FIGURE 9: ASPLIT-REGISTER READ-TRANSFER CYCLEAFTERA

SPLIT-REGISTER READ-TRANSFER CYCLE

SERIAL-ACCESS OPERATION

the preceding transfer operation is a write- or pseudo-write-

transfer operation, the SAM port is in the input mode.

Serial data can be read out of or written into SAM by clock-

ing SC starting at the tap point loaded by the preceding transfer

cycle, proceeding sequentially to the most significant bit (bit

511), then wrapping around to the least

The serial-read and serial-write operations can be performed

through the SAM port simultaneously and asynchronously

with DRAM operations except during transfer operations. The

preceding transfer operation determines the input or output

state of the SAM port. If the preceding transfer operation is a

read-transfer operation, the SAM port is in the output mode. If

significant bit (bit 0) (see Figure 10).

FIGURE 10: SERIAL POINTER DIRECTION FOR SERIAL READ/WRITE

the inactive half during this period, the serial pointer points

next to the tap-point location loaded by that split register (see

Figure 11, Case I). If there is no split-register read transfer to the

inactive half during this period, the serial pointer points next to

bit 256 or bit 0, respectively (see Figure 11, Case II).

For split-register read-transfer operation, serial data can be read

out from the active half of SAM by clocking SC starting at the

tap point loaded by the preceding split-register-transfer cycle,

then proceeding sequentially to the most significant bit of the

half, bit 255 or bit 511. If there is a split-register-read transfer to

FIGURE 11: SERIAL POINTER FOR SPLIT-REGISTER READ

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

SMJ44C251B/MT42C4256

Rev. 0.1 12/03

15

AUSTIN [ AUSTIN SEMICONDUCTOR ]

AUSTIN [ AUSTIN SEMICONDUCTOR ]