VRAM

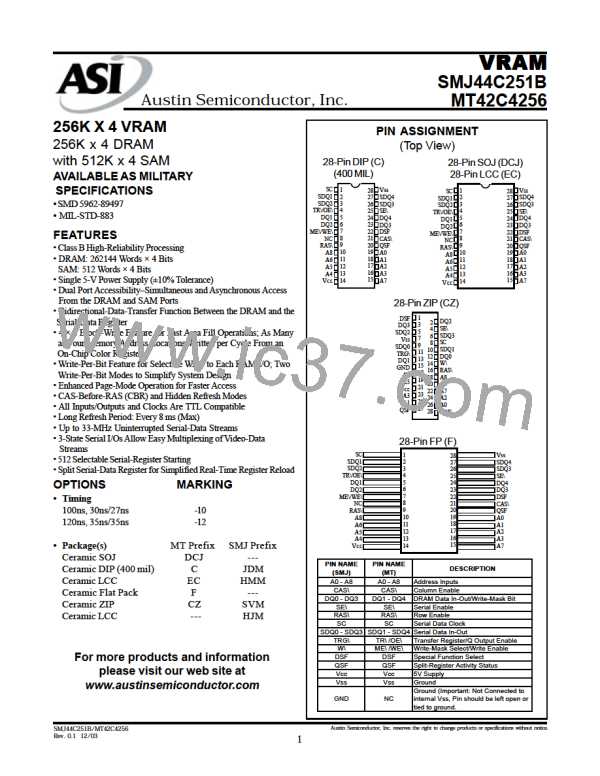

SMJ44C251B

MT42C4256

Austin Semiconductor, Inc.

NORMAL-READ TRANSFER

A normal-read transfer can be performed in three ways:

early-load read transfer, real-time or midline-load read transfer,

and late-load read transfer. Each of these offers the flexibility of

controlling the TRG\ trailing edge in the read-transfer cycle

(see Figure 7).

(refer to Figure 7)

address bits (A0–A8) are latched at the falling edge of CAS\ to

select one of the SAM’s 512 available tap points where the

serial data is read out.

FIGURE 6: NORMAL-WRITE-TRANSFER-CYCLE TIMING

FIGURE 7: NORMAL-READ-TRANSFER TIMINGS

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

SMJ44C251B/MT42C4256

Rev. 0.1 12/03

13

AUSTIN [ AUSTIN SEMICONDUCTOR ]

AUSTIN [ AUSTIN SEMICONDUCTOR ]