ASAHI KASEI

[AK4115]

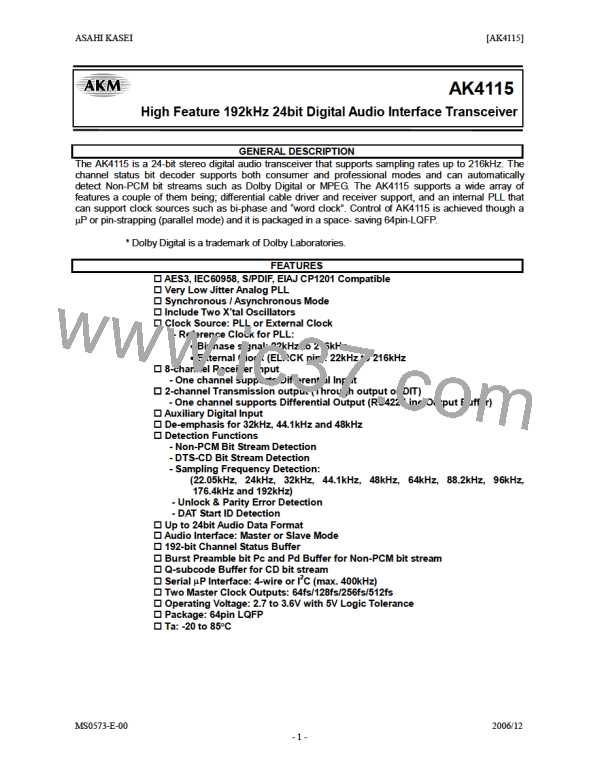

Register Map

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

00H CLK & Power Down Control CS12

BCU

DIF2

CM1

DIF1

CM0

DIF0

OCKS1 OCKS0

DEAU DEM1

PWN

DEM0

RSTN

ACKS

01H Format & De-em Control

02H Input/ Output Control 0

03H Input/ Output Control 1

04H INT0 MASK

AES3

TX1E

EFH1

OPS12 OPS11 OPS10

EFH0 UDIT BCU_IO

TX0E

DIT

OPS02 OPS01 OPS00

IPS2 IPS1 IPS0

MQIT0 MAUT0 MCIT0 MULK0 MV0

MQIT1 MAUT1 MCIT1 MULK1 MV1

MSTC0 MAUD0 MPAR0

MSTC1 MAUD1 MPAR1

05H INT1 MASK

06H DAT Mask & DTS Detect

07H Receiver Status 0

08H Receiver Status 1

09H Receiver Status 2

0AH Clock Control

DIV

QINT

FS3

XMCK

AUTO

FS2

0

FAST

DCNT DTS16 DTS14 MDAT1 MDAT0

STC AUDION PAR

CINT UNLCK VRX

FS1

0

FS0

0

PEM

0

DAT

0

DTSCD NPCM

0

QCRC

XSEL

CCRC

PSEL

VTX

CR0

WSYNC

MCK2E MCK1E ASYNC

TX1NE

0

0BH TX Control

MSEL ECKS1 ECKS0 EDIF1

EDIF0 CTRAN CCRE

0CH RX Channel Status Byte 0

CR7

CR6

CR5

CR4

CR3

CR2

CR1

•

•

•

•

•

•

•

•

•

•

CR191

CR190

CR189

CR188

CR187

CR186

CR185

CR184

23H RX Channel Status Byte 23

24H TX Channel Status Byte 0

CT7

CT6

CT5

CT4

CT3

CT2

CT1

CT0

•

•

•

CT191

PC7

PC15

PD7

PD15

Q9

•

•

•

•

•

•

•

CT184

PC0

PC8

PD0

PD8

Q2

3BH TX Channel Status Byte 23

3CH Burst Preamble Pc Byte 0

3DH Burst Preamble Pc Byte 1

3EH Burst Preamble Pd Byte 0

3FH Burst Preamble Pd Byte 1

40H Q-subcode Address / Control

41H Q-subcode Track

CT190 CT189 CT188 CT187 CT186 CT185

PC6

PC14

PD6

PD14

Q8

PC5

PC13

PD5

PD13

Q7

PC4

PC12

PD4

PD12

Q6

PC3

PC11

PD3

PD11

Q5

PC2

PC10

PD2

PD10

Q4

PC1

PC9

PD1

PD9

Q3

Q17

Q25

Q33

Q41

Q49

Q57

Q65

Q73

Q81

0

Q16

Q24

Q32

Q40

Q48

Q56

Q64

Q72

Q80

0

Q15

Q23

Q31

Q39

Q47

Q55

Q63

Q71

Q79

0

Q14

Q22

Q30

Q38

Q46

Q54

Q62

Q70

Q78

0

Q13

Q21

Q29

Q37

Q45

Q53

Q61

Q69

Q77

0

Q12

Q20

Q28

Q36

Q44

Q52

Q60

Q68

Q76

0

Q11

Q19

Q27

Q35

Q43

Q51

Q59

Q67

Q75

CTX

Q10

Q18

Q26

Q34

Q42

Q50

Q58

Q66

Q74

0

42H Q-subcode Index

43H Q-subcode Minute

44H Q-subcode Second

45H Q-subcode Frame

46H Q-subcode Zero

47H Q-subcode ABS Minute

48H Q-subcode ABS Second

49H Q-subcode ABS Frame

4AH Optional Control

Notes:

When PDN pin goes “L”, the registers are initialized to their default values.

When RSTN bit goes “0”, the internal timing is reset and the registers are initialized to their default values.

All data can be written to the register even if PWN bit is “0”.

Data must not be written to addresses 4BH through FFH.

MS0573-E-00

2006/12

- 48 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]