8

Figure 7. Simplified Digital Noise Filter Logic.

Figure 8. Signal Propagation through Digital Noise Filter.

the internal position counter. In

Design Considerations

Quadrature Decoder

the case of the HCTL-2020, the

signals also go to external pins 5

and 16 respectively.

The designer should be aware

that the operation of the digital

filter places a timing constraint

on the relationship between

incoming quadrature signals and

the external clock. Figure 8

shows the timing waveform with

an incremental encoder input.

Since an input has to be stable

for three rising clock edges, the

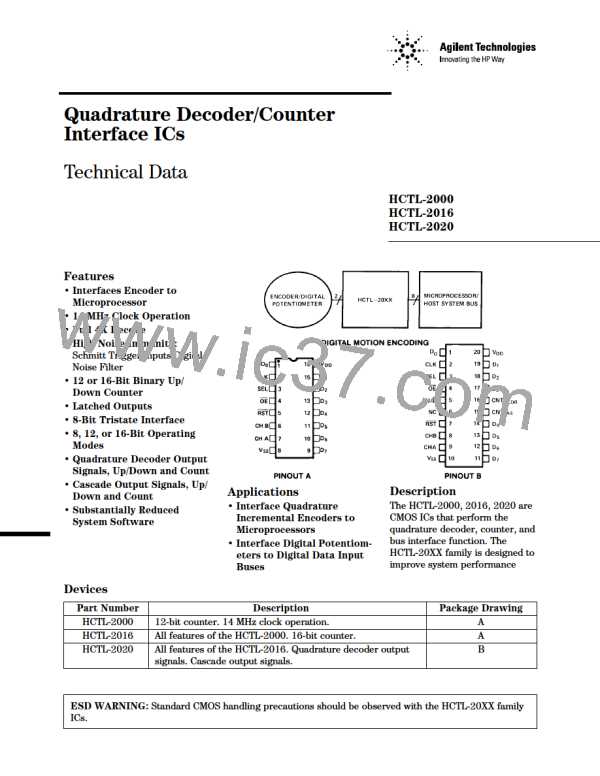

The quadrature decoder decodes

the incoming filtered signals into

count information. This circuitry

multiplies the resolution of the

input signals by a factor of four

(4X decoding). When using an

encoder for motion sensing, the

user benefits from the increased

resolution by being able to

Figure 9 shows the quadrature

states and the valid state transi-

tions. Channel A leading channel

B results in counting up. Channel

B leading channel A results in

counting down. Illegal state

transitions, caused by faulty

encoders or noise severe enough

to pass through the filter, will

produce an erroneous count.

provide better system control.

encoder pulse width (t - low or

E

high) has to be greater than three

The quadrature decoder samples

the outputs of the CHA and CHB

filters. Based on the past binary

state of the two signals and the

present state, it outputs a count

signal and a direction signal to

clock periods (3t

). This

CLK

guarantees that the asynchronous

input will be stable during three

consecutive rising clock edges. A

realistic design also has to take

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]