12

General Interfacing

read the high order 4 or 8 bits

from the latch and then read the

low order 8 bits from the latch.

Meanwhile, the counter can

continue to keep track of the

quadrature states from the CHA

and CHB input signals.

For proper operation of the

inhibit logic during a two-byte

read, OE and SEL must be

synchronous with CLK due to

the falling edge sampling of OE

and SEL.

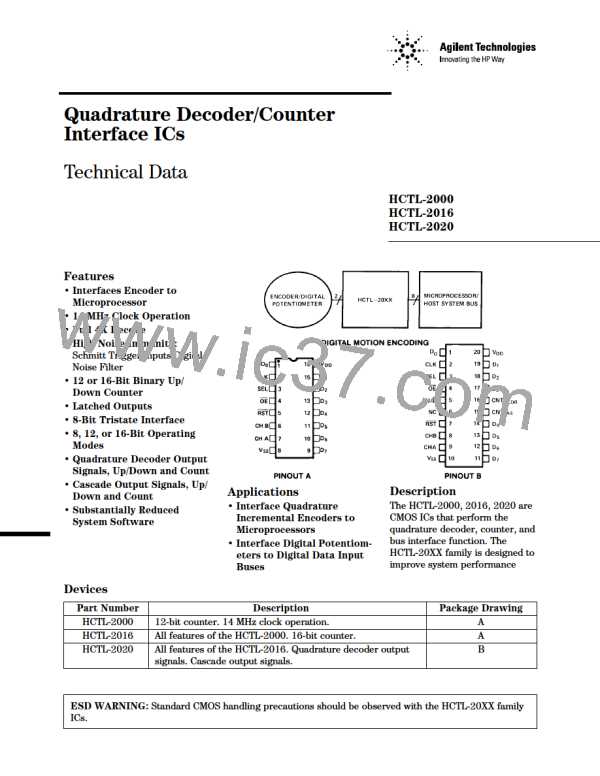

The 12-bit (HCTL-2000) or 16-bit

(HCTL-2016/2020) latch and

inhibit logic allows access to 12

or 16 bits of count with an 8-bit

bus. When only 8-bits of count

are required, a simple 8-bit (1-

byte) mode is available by

holding SEL high continuously.

This disables the inhibit logic. OE

provides control of the tri-state

bus, and read timing is shown in

Figures 2 and 3.

The internal inhibit logic on the

HCTL-20XX family inhibits the

transfer of data from the counter

to the position data latch during

the time that the latch outputs are

being read. The inhibit logic

Figure 11 shows the simplified

inhibit logic circuit. The

operation of the circuitry is

illustrated in the read timing

shown in Figure 13.

allows the microprocessor to first

*OE can consist of two short low pulses, as well as one long pulse, and still satisfy

the inhibit logic sequence. During the time that OE is high, the data lines are tri-seated.

Figure 13. Typical Interface Timing.

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]