11

INTERNAL COUNTER

ROLL OVER

CLK

FF 00

CHA

CHB

*

*

FILT

FILT

START INHIBIT

U/D

CNT

*

DCDR

CNT

CAS

COUNT

FFFDH

FFFEH

FFFFH

0000H

FFFFH

FFFDH

*CHA

AND CHB

ARE THE OUTPUTS

FILT

FILT

OF THE DIGITAL NOISE FILTER (SEE FIGURES 7 AND 8).

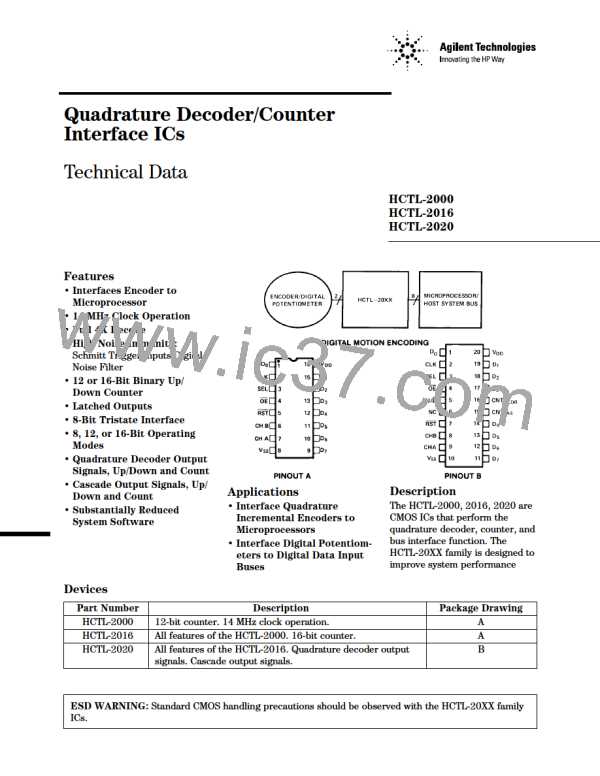

Figure 12. Decode and Cascade Output Diagram.

Cascade Considerations

(HCTL-2020 Only)

will be generated with some delay

count in the inhibited internal

latch. The cascade pulse that

occurs during the clock cycle

when the read begins gets

counted by the external counter

and is not lost.

after the rising clock edge (t

There will be additional

).

CHD

The HCTL-2020’s cascading

system allows for position reads

of more than two bytes. These

reads can be accomplished by

latching all of the bytes and then

reading the bytes sequentially

over the 8-bit bus. It is assumed

here that, externally, a counter

followed by a latch is used to

count any count that exceeds 16

bits. This configuration is

propagation delays through the

external counters and registers.

Meanwhile, with SEL and OE low

to start the read, the internal

latches are inhibited at the falling

edge and do not update again till

the inhibit is reset. If the CNTCAS

pulse now toggles the external

counter and this count gets

latched a major count error will

occur. The count error is because

the external latches get updated

when the internal latch is

For example, suppose the HCTL-

2020 count is at FFFFH and an

external counter is at F0H, with

the count going up. A count

occurring in the HCTL-2020 will

cause the counter to roll over and

a cascade pulse will be generated.

A read starting on this clock cycle

will show FFFFH from the HCTL-

2020. The external latch should

read F0H, but if the host latches

the count after the cascade signal

propagates through, the external

latch will read F1H.

compatible with the HCTL-2020

internal counter/latch

combination.

inhibited.

Consider the sequence of events

for a read cycle that starts as the

HCTL-2020’s internal counter

rolls over. On the rising clock

edge, count data is updated in the

internal counter, rolling it over. A

Valid data can be ensured by

latching the external counter data

when the high byte read is started

(SEL and OE low). This latched

external byte corresponds to the

count-cascade pulse (CNT

)

CAS

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]

AGILENT [ AGILENT TECHNOLOGIES, LTD. ]