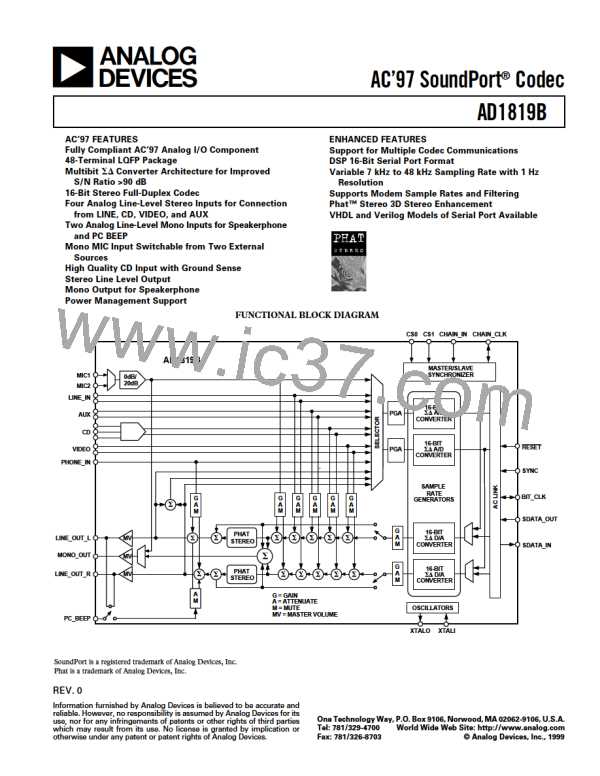

AD1819B

The AC-Link protocol provides for a special 16-bit time slot (Slot 0) wherein each bit conveys a valid tag for its corresponding time

slot within the current audio frame. A “1” in a given bit position of Slot 0 indicates that the corresponding time slot within the cur-

rent audio frame has been assigned to a data stream, and contains valid data. If a slot is “tagged” invalid, it is the responsibility of the

source of the data, (AD1819B for the input stream, AC’97 controller for the output stream), to stuff all bit positions with 0s during

that slot’s active time. The AD1819B stuffs all invalid slots with zeros and ignores invalid input slots.

Additionally, for power savings, all clock, sync, and data signals can be halted.

For multiple codec operations, the AD1819B supports an enhanced mode for communicating with up to two additional codecs. The

Slave 1 AD1819B codec uses Slots 5 and 6, while Slave 2 uses Slots 7 and 8 as shown in the following diagram.

ENHANCED MODE

SLOT # ....

1

2

3

4

5

6

7

8

9

10

11

12

SYNC

CMD

ADR

CMD

DATA

PCM

LEFT

PCM

RIGHT

PCM

RIGHT

PCM

RIGHT

PCM

LEFT

PCM

LEFT

OUTGOING STREAMS

INCOMING STREAMS

TAG

TAG

RSRVD RSRVD RSRVD RSRVD

PCM

LEFT

PCM

RIGHT

PCM

LEFT

PCM

RIGHT

PCM

LEFT

PCM

RIGHT

STATUS STATUS

ADR DATA

RSRVD

RSRVD RSRVD RSRVD

SLAVE 2

DATA PHASE

SLAVE 1

TAG

PHASE

Figure 9. Standard Bidirectional Audio Frame

AC-Link Audio Output Frame (SDATA_OUT)

The audio output frame data streams correspond to the multiplexed bundles of all digital output data targeting AD1819B’s DAC

inputs and control registers. As briefly mentioned earlier, each audio output frame supports up to twelve 20-bit outgoing data time

slots. Slot 0 is a special reserved time slot containing 16 bits that are used for AC-Link protocol infrastructure.

Within Slot 0 the first bit is a global bit (SDATA_OUT Slot 0, Bit 15), which flags the validity for the entire audio frame. If the

“Valid Frame” bit is a 1, this indicates that the current audio frame contains at least one slot time of valid data. The next 12-bit

positions sampled by AC’97 indicate which of the corresponding 12 time slots contain valid data. In this way input DAC data

streams of differing sample rates can be transmitted across the AC-Link at its fixed 48 kHz audio frame rate. The following diagram

illustrates the time-slot-based AC-Link protocol.

TAG PHASE

DATA PHASE

20.8s (48kHz)

12.2888MHz

SYNC

81.4ns

BIT_CLK

CODEC

READY

SLOT(12)

19

0

19

0

19

0

19

0

SLOT(1) SLOT(2)

“0”

“0”

“0”

SDATA_IN

SLOT 1

SLOT 2

SLOT 3

SLOT 12

TIME SLOT “VALID”

BITS

(1) = TIME SLOT CONTAINS VALID PCM DATA

END OF PREVIOUS

AUDIO FRAME

Figure 10. AC-Link Audio Output Frame

A new audio output frame begins with a low-to-high transition of SYNC. SYNC is synchronous to the rising edge of BIT_CLK. On

the immediately following falling edge of BIT_CLK, the AD1819B samples the assertion of SYNC. This falling edge marks the time

when both sides of AC-Link are aware of the start of a new audio frame. On the next rising edge of BIT_CLK, the AC’97 controller

transitions SDATA_OUT into the first bit position of Slot 0 (Valid Frame Bit). Each new bit position is presented to AC-Link on a

rising edge of BIT_CLK, and subsequently sampled by AD1819B on the following falling edge of BIT_CLK. This sequence ensures

that data transitions, and subsequent sample points for both incoming and outgoing data streams are time aligned.

REV. 0

–19–

ADI [ ADI ]

ADI [ ADI ]