prior to the start of the bulk transfer, the BU-65550 and

BU-65551 may be configured to issue an interrupt request only

after it has received the anticipated number of valid Data Words

to the designated subaddress.

most recent valid block of received Data Words will always be

readily accessible to the host processor.As a means of ensuring

data consistency, the host processor is able to reliably access

the most recent valid, received Data Word block by performing

the following sequence:

SUBADDRESS DOUBLE BUFFERING MODE

(1) Disable the double buffering for the respective subad-

dress by the Subaddress Control Word. That is, temporarily

switch the subaddresses' memory management scheme to

the Single Message mode.

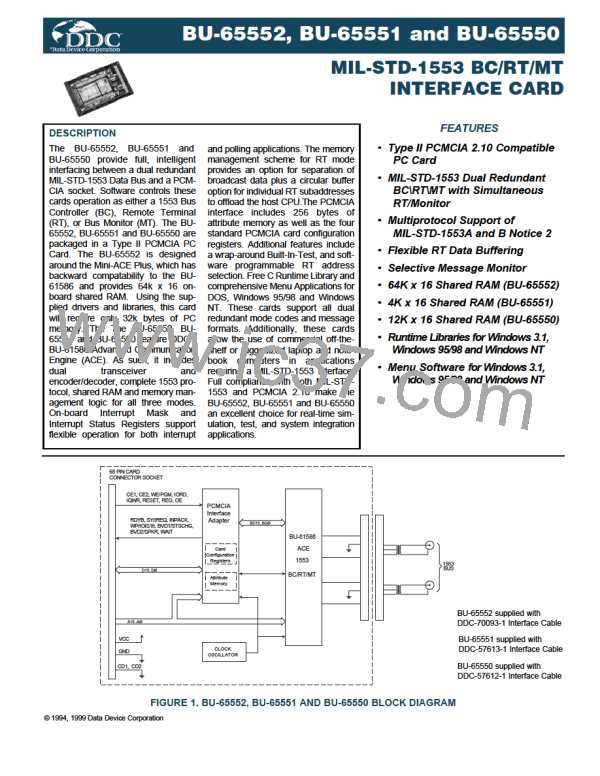

For receive (and broadcast) subaddresses, the BU-65552, BU-

65551 and BU-65550 RT offer a third memory management

option, Subaddress Double Buffering. Subaddress double

buffering provides a means of ensuring data consistency.

FIGURE 12 illustrates the RT Subaddress Double Buffering

scheme. Like the Single Message and Circular Buffer modes,

the Double Buffering mode may be selected on a subaddress

basis by means of the Subaddress Control Word. The purpose

of the Double Buffering mode is to provide the host processor a

convenient means of accessing the most recent, valid data

received to a given subaddress. This serves to ensure the high-

est possible degree of data consistency by allocating two 32-bit

Data Word blocks for each individual receive (and/or broadcast)

subaddress.

(2) Read the current value of the receive (or broadcast) sub-

address's Lookup Table pointer. This points to the current

"active" Data Word block. By inverting bit 5 of this pointer

value, it is possible to locate the start of the "inactive" Data

Word block. This block will contain the Data Words received

during the most recent valid message to the subaddress.

(3) Read out the words from the "inactive" (most recent) Data

Word Block.

(4) Re-enable the Double Buffering mode for the respective

subaddress by the Subaddress Control Word.

At a given point in time, one of the two blocks will be designated

as the "active" 1553 data block while the other will be designat-

ed as the "inactive" block. The Data Words from the next receive

message to that subaddress will be stored in the "active" block.

Upon completion of the message, provided that the message

was valid and Subaddress Double Buffering is enabled, the BU-

65552, BU-65551 and BU-65550 will automatically switch the

"active" and "inactive" blocks for the respective subaddress. The

ACE accomplishes this by toggling bit 5 of the subaddresses'

Lookup Table Pointer and rewriting the pointer. As a result, the

RT INTERRUPTS

As in BC mode, the BU-65552, BU-65551 and BU-65550 RT

provide many maskable interrupts. RT interrupt conditions

include End of (every) Message, Message Error, Selected

Subaddress (Subaddress Control Word) Interrupt, Circular

Buffer Rollover, Selected Mode Code Interrupt, and Stack

Rollover.

CONFIGURATION

REGISTER

STACK

POINTERS

DESCRIPTOR

STACK

LOOK-UP

TABLES

15

13

0

DATA

BLOCKS

CURRENT

AREA B/A

BLOCK STATUS WORD

TIME TAG WORD

X..X 0 YYYYY

DATA

BLOCK 0

DATA BLOCK POINTER

DATA BLOCK POINTER

X..X 1 YYYYY

RECEIVED COMMAND

WORD

DATA

BLOCK 1

RECEIVE DOUBLE

BUFFER ENABLE

MSB

SUBADDRESS

CONTROL WORD

FIGURE 12. RT MEMORY MANAGEMENT: SUBADDRESS DOUBLE BUFFERING MODE

21

ETC [ ETC ]

ETC [ ETC ]