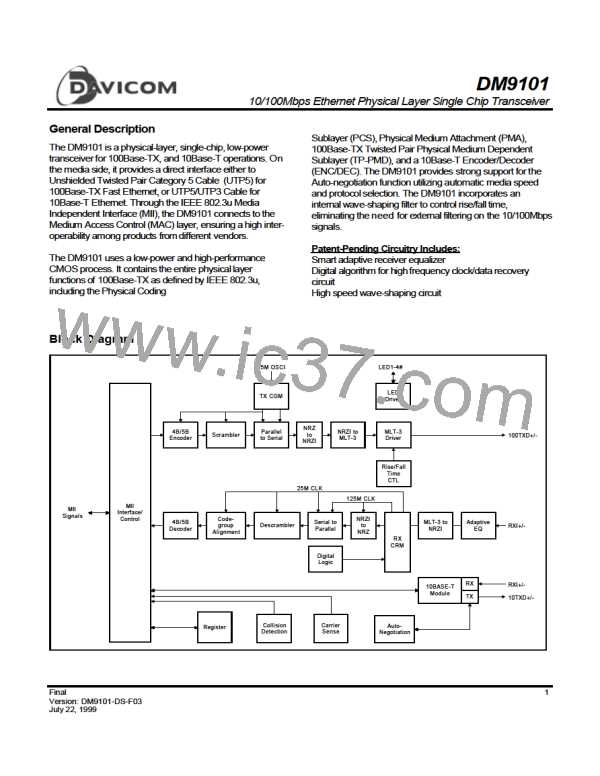

DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

Pin Description (continued)

Pin No.

LQFP QFP

PHY Address Interface:

Pin Name

I/O

Description

PHYAD[4:0] provides up to 32 unique PHY address. An address selection of all zeros (00000) will result in a

PHY isolation condition. See the isolate bit description in the BMCR, address 00.

PHY Address 0:

81

82

83

86

87

83

84

85

88

89

PHYAD0

PHYAD1

PHYAD2

PHYAD3

PHYAD4

I

I

I

I

I

PHY address bit 0 for multiple PHY address applications. The

status of this pin is latched into Register 17, bit 8 during power

up/reset.

PHY Address 1:

PHY address bit 1 for multiple PHY address applications. The

status of this pin is latched into Register 17, bit 7 during power

up/reset.

PHY Address 2:

PHY address bit 2 for multiple PHY address applications. The

status of this pin is latched into Register 17, bit 6 during power

up/reset.

PHY Address 3:

PHY address bit 3 for multiple PHY address applications. The

status of this pin is latched into Register 17, bit 5 during power

up/reset.

PHY Address 4:

PHY address bit 4 for multiple PHY address applications. The

status of this pin is latched into Register 17, bit 4 during power

up/reset.

Miscellaneous

No Connect:

Leave these pins unconnected (floating).

1-3,

17, 18,

44,

2 - 5,

19, 20,

46

NC

100

Bandgap Voltage Reference:

33

35

BGREF

I

Connect a 6.01KΩ, 1% resistor between this pin and the BGRET

pin to provide an accurate current reference for the DM9101.

Bandgap Voltage Reference Return:

Return pin for 6.01KΩ resistor connection.

Tri-state Digital Output Pins:

34

39

36

41

BGRET

TRIDRV

I

I

When set high, all digital output pins are set to a high impedance

state, and I/O pins, go to input mode.

Reset: Active Low input that initializes the DM9101. It should

remain low for 30ms after VCC has stabilized at 5Vdc (normal)

before it transitions high.

79

80

81

82

RESET#

I

I

Test Mode Control Pin:

TESTMODE

TESTMODE=0: Normal operating mode.

TESTMODE=1: Enable test mode.

10

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]