DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

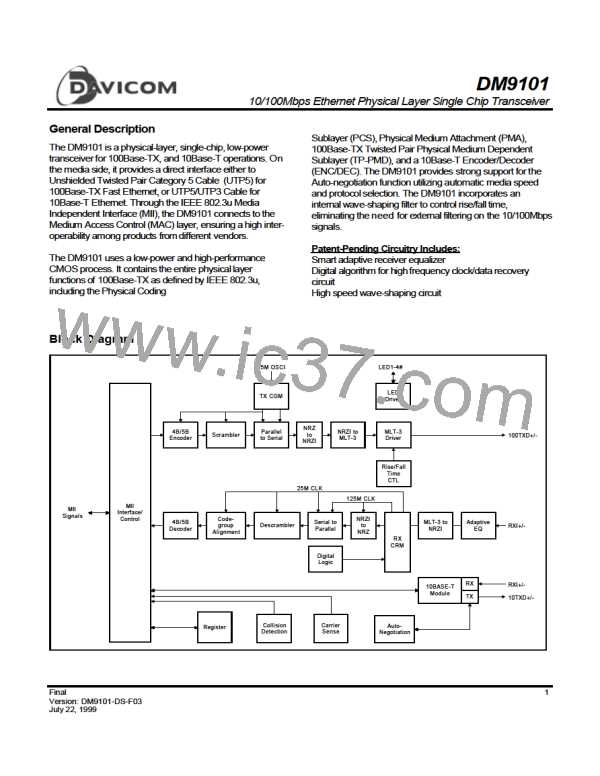

The DM9101 performs all PCS (Physical Coding

Sublayer), PMA (Physical Media Access), TP-PMD

(Twisted Pair Physical Medium Dependent) sublayer,

10Base-T Encoder/Decoder, and Twisted Pair Media

Access Unit (TPMAU) functions. Figure 1 shows the major

functional blocks implemented in the DM9101.

Functional Description

The DM9101 Fast Ethernet single-chip transceiver,

provides the functionality as specified in IEEE 802.3u,

integrates a complete 100Base-TX module and a

complete 10Base-T module. The DM9101 provides a

Media Independent Interface (MII) as defined in the IEEE

802.3u standard (Clause 22).

100Base-TX

Transmitter

100Base-TX

Receiver

10Base-T

Tranceiver

MII Interface

Carrier

Sense

Collision

Detection

Auto

Negotiation

MII Serial

Management

Interface

Figure 1

•

TXD (transmit data) is a nibble (4 bits) of data that are

driven by the reconciliation sublayer synchronously with

respect to TX_CLK. For each TX_CLK period which

TX_EN is asserted, TXD (3:0) are accepted for

transmission by the PHY.

MII Interface

The DM 9101 provides a Media Independent Interface (MII)

as defined in the IEEE 802.3u standard (Clause 22).

The purpose of the MII interface is to provide a simple, easy

to implement connection between the MAC Reconciliation

layer and the PHY. The MII is designed to make the

differences between various media transparent to the MAC

sublayer.

The MII consists of a nibble wide receive data bus, a nibble

wide transmit data bus, and control signals to facilitatedata

transfers between the PHY and the Reconciliation layer.

•

•

TX_CLK (transmit clock) output to the MAC

reconciliation sublayer is a continuous clock that

provides the timing reference for the transfer of the

TX_EN, TXD, and TX_ER signals.

TX_EN (transmit enable) input from the MAC

reconciliation sublayer to indicate nibbles are being

presented on the MII for transmission on the physical

medium.

12

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]