DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

100Base-TX Operation

These two busses include various controlsand signal

indications that facilitate data transfers between the

DM9101 and the Reconciliation layer.

The 100Base-TX transmitter receives 4-bit nibble data

clocked in at 25MHz at the MII, and outputs a scrambled

5-bit encoded MLT-3 signal to the media at 100Mbps. The

on-chip clock circuit converts the 25MHz clock into a

125MHz clock for internal use.

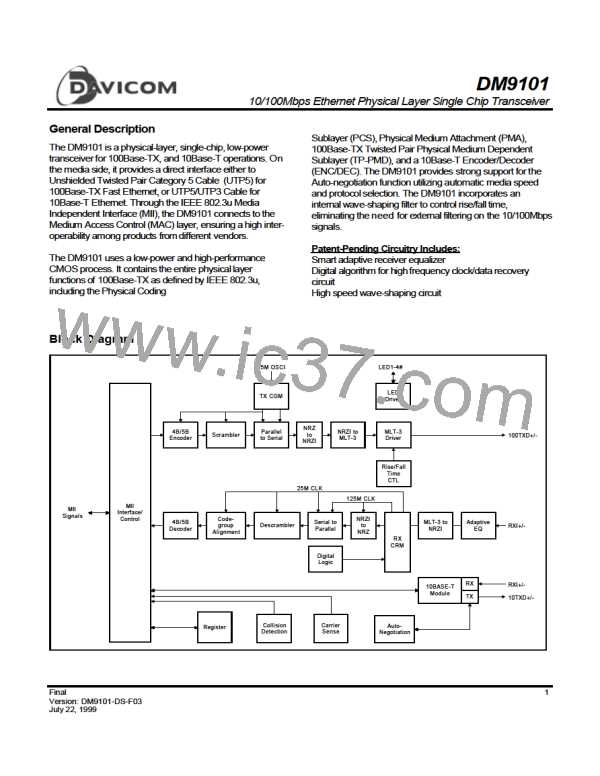

100Base-TX Transmit

The 100Base-TX transmitter consists of the functional

blocks shown in figure 3. The 100Base-TX transmit

section converts 4-bit synchronous data provided by the

MII to a scrambled MLT-3 125 million symbols per second

serial data stream.

The IEEE 802.3u specification defines the Media

Independent Interface. The interface specification defines

a dedicated receive data bus and a dedicated transmit

data bus.

25M OSCI

LED1-4#

LED

Driver

TX CGM

TXCLK

TXEN

TXER

NRZ

to

NRZI

4B/5B

Encoder

Parallel

to Serial

NRZI to

MLT-3

MLT-3

Driver

100TXD+/-

Scrambler

Transmit

MII

Interface/

Control

Rise/Fall

Time

CTL

RX

TX

RXI+/-

10BASE-T

Module

10TXD+/-

TXD (3:0

Collision

Detection

Carrier

Sense

Register

Figure 3

14

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]