®

PMD-100

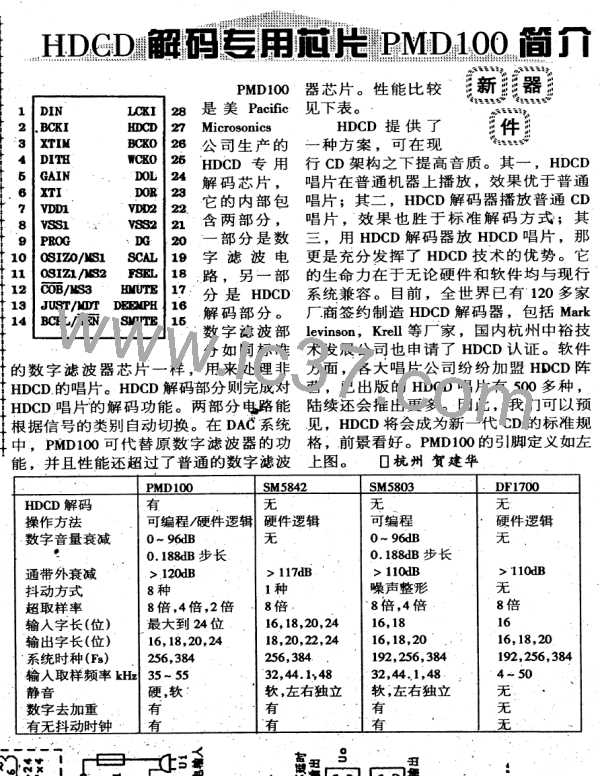

PMD-100 Process Decoder

Data Output

The output data format is determined by the oversampling rate and the word length. The oversampling rate of 2 Fs, 4 Fs,

or 8 Fs is selected by OVER1 and OVER0. The default in Stand-Alone Mode is 8Fs. The output word length of 16, 18, 20,

or 24 bits is selected by OSIZ1 and OSIZ0. This selection also determines the number of pulses on the BCKO bit clock

output. Note that if OVER0 and OVER1 are set to 2 Fs, then OSIZ0 and OSIZ1 must be set to 24 bits and DITH

must be set low (dither disabled).

Refer to the Output Timing diagrams below; DOL and DOR are the left and right channel data outputs. Output data is

MSB first and is selectable by COB to be either 2’s complement or complementary offset binary. Data is clocked out on the

falling edge and latched on the rising edge of the BCKO bit clock output. There are as many bit clock rising edges as there

are output data bits. The data word start is marked by the rising or falling edge (selected by WCPL) of the word clock

output WCKO. The default setting for WCKO is the falling edge. After the last bit of the data word is output, the BCKO

signal is halted, and remains in this mode until WCKO changes state and the DAC initiates D/A conversion. This “Silent

Conversion” minimizes conversion jitter and ground bounce by allowing time for the DAC substrate noise to settle out

prior to conversion.

There are 32 deglitch intervals dividing the output sampling period. In Stand Alone Mode DG goes low at the beginning

of the 15th interval and high at the beginning of the 31st interval. In Program Mode variable deglitch timing is available.

The falling and rising edges can be programmed to occur at any of the 32 deglitch intervals as defined by DGL4, DGL3,

DGL2, DGL1, and DGL0 (falling edge) and by DGH4, DGH3, DGH2, DGH1, and DGH0 (rising edge). (See: Program

Mode).

8 Fs Output Timing

Stand-Alone Mode (PROG Pin = 0)

WCKO

Pacific Microsonics, Inc.

8

32990 Alvarado Niles Road, Suite 910

Union City , CA 94587

Phone (510) 475-8000

Fax (510) 475-8005

ETC [ ETC ]

ETC [ ETC ]