R

Platform Flash In-System Programmable Configuration PROMs

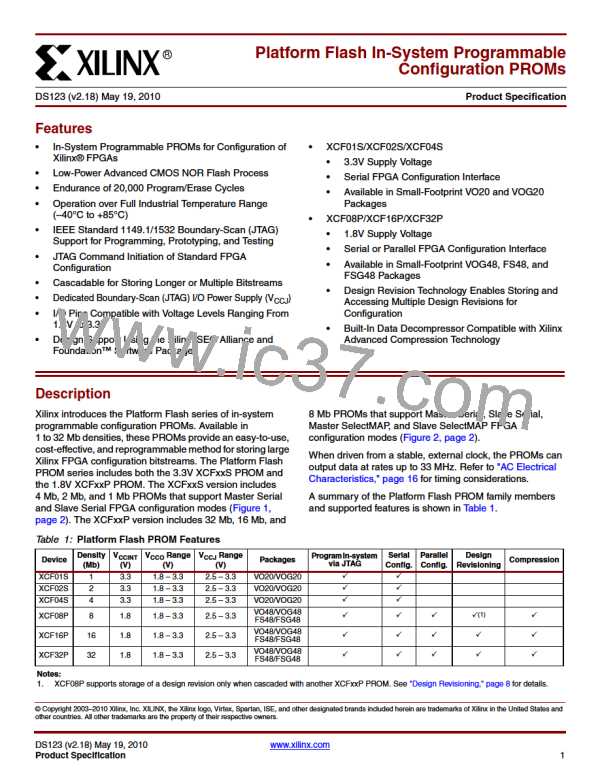

XCFxxP PROM as Configuration Master with Internal Oscillator as Clock Source

X-Ref Target - Figure 9

CE

T

HCE

T

HOE

OE/RESET

CLKOUT

T

CEC

T

SB

T

HB

T

T

T

DDC

T

CDD

COH

OEC

T

T

CECF

OECF

BUSY

T

OE

(optional)

T

CE

DATA

T

CF

T

EOH

T

CFC

HXT

T

DF

T

HCF

CF

EN_EXT_SEL

REV_SEL[1:0]

T

T

T

SXT

T

HXT

SXT

T

T

T

T

HRV

SRV

HRV

SRV

Note: Typically, 8 CLKOUT cycles are output after CE rising edge, before CLKOUT

tristates, if OE/RESET remains high, and terminal count has not been reached.

ds123_26_110707

XCF08P, XCF16P,

XCF32P

Symbol

Description

Units

Min

Max

CF hold time to guarantee design revision selection is sampled

when VCCO = 3.3V or 2.5V(12)

300

300

300

THCF

CF hold time to guarantee design revision selection is sampled

when VCCO = 1.8V(12)

300

CF to data delay when VCCO = 3.3V or 2.5V

–

–

–

–

–

–

5

5

–

–

–

–

–

–

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TCF

CF to data delay when VCCO = 1.8V

OE/RESET to data delay(6) when VCCO = 3.3V or 2.5V

OE/RESET to data delay(6) when VCCO = 1.8V

CE to data delay(5) when VCCO = 3.3V or 2.5V

CE to data delay(5) when VCCO = 1.8V

25

25

25

25

–

TOE

TCE

Data hold from CE, OE/RESET, or CF when VCCO = 3.3V or 2.5V

TEOH

Data hold from CE, OE/RESET, or CF when VCCO = 1.8V

–

CE or OE/RESET to data float delay(2) when VCCO = 3.3V or 2.5V

CE or OE/RESET to data float delay(2) when VCCO = 1.8V

OE/RESET to CLKOUT float delay(2) when VCCO = 3.3V or 2.5V

OE/RESET to CLKOUT float delay(2) when VCCO = 1.8V

CE to CLKOUT float delay(2) when VCCO = 3.3V or 2.5V

CE to CLKOUT float delay(2) when VCCO = 1.8V

CE hold time (guarantees counters are reset)(5) when VCCO = 3.3V or 2.5V

CE hold time (guarantees counters are reset)(5) when VCCO = 1.8V

OE/RESET hold time (guarantees counters are reset)(6) when VCCO = 3.3V or 2.5V

OE/RESET hold time (guarantees counters are reset)(6) when VCCO = 1.8V

45

45

TDF

TOECF

TCECF

THCE

THOE

2000

2000

2000

2000

–

–

–

–

DS123 (v2.18) May 19, 2010

www.xilinx.com

Product Specification

21

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]