X4043/45

Acknowledge Polling

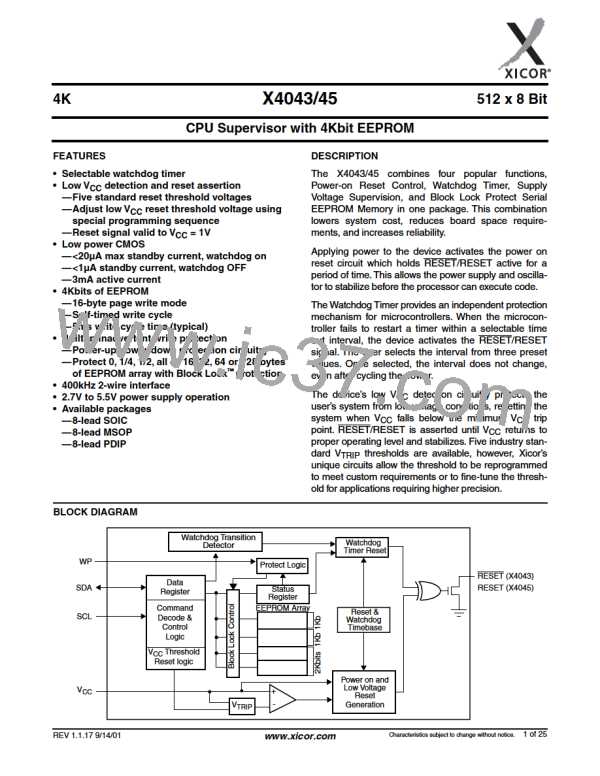

Figure 13. Acknowledge Polling Sequence

The disabling of the inputs during nonvolatile cycles

can be used to take advantage of the typical 5kHz write

cycle time. Once the stop condition is issued to indicate

the end of the master’s byte load operation, the device

initiates the internal nonvolatile cycle. Acknowledge

polling can be initiated immediately. To do this, the mas-

ter issues a start condition followed by the slave

address byte for a write or read operation. If the device

is still busy with the nonvolatile cycle then no ACK will

be returned. If the device has completed the write oper-

ation, an ACK will be returned and the host can then

proceed with the read or write operation. Refer to the

flow chart in Figure 13.

Byte Load Completed

by Issuing STOP.

Enter ACK Polling

Issue START

Issue Slave Address

Byte (Read or Write)

Issue STOP

NO

ACK

Returned?

Serial Read Operations

YES

Read operations are initiated in the same manner as

write operations with the exception that the R/W bit of

the slave address byte is set to one. There are three

basic read operations: Current Address Reads, Ran-

dom Reads, and Sequential Reads.

NO

Nonvolatile Cycle

Complete. Continue

Command

Issue STOP

Current Address Read

YES

Internally the device contains an address counter that

maintains the address of the last word read incre-

mented by one. Therefore, if the last read was to

address n, the next read operation would access data

from address n+1. On power up, the address of the

address counter is undefined, requiring a read or write

operation for initialization.

Continue Normal

Read or Write

Command Sequence

PROCEED

Upon receipt of the slave address byte with the R/W bit

set to one, the device issues an acknowledge and then

transmits the eight bits of the data byte. The master ter-

minates the read operation when it does not respond

with an acknowledge during the ninth clock and then

issues a stop condition. Refer to Figure 13 for the

address, acknowledge, and data transfer sequence.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read oper-

ation, the master must either issue a stop condition dur-

ing the ninth cycle or hold SDA HIGH during the ninth

clock cycle and then issue a stop condition.

Figure 14. Current Address Read Sequence

S

t

S

t

o

p

Slave

Address

Signals from

the Master

a

r

t

SDA Bus

1

A

C

Signals from

the Slave

Data

K

Characteristics subject to change without notice. 11 of 25

REV 1.1.17 9/14/01

www.xicor.com

XICOR [ XICOR INC. ]

XICOR [ XICOR INC. ]