TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

7.6.5 FLAG Registers

表 7-137 lists the memory-mapped registers for the FLAG registers. All register offset addresses not listed in 表

7-137 should be considered as reserved locations and the register contents should not be modified.

FLAG Register

表 7-137. FLAG Registers

Offset

A0h

A1h

A2h

A3h

A4h

A5h

A6h

A7h

A8h

A9h

AAh

ABh

ACh

ADh

AEh

AFh

Acronym

Register Name

Section

Go

FLAG_ERR

Device Error Flag Register

FLAG_STATUS

FLAG_ADC

Device Status Flag Register

Go

Selected Channel ADC Measurement Result

OUTAn, OUTBn Single-LED Short Error FLAG

OUTCn, OUTDn Single-LED Short Error FLAG

OUTEn, OUTFn Single-LED Short Error FLAG

OUTGn, OUTHn Single-LED Short Error FLAG

OUTAn, OUTBn LED Open Error FLAG

OUTCn, OUTDn LED Open Error FLAG

OUTEn, OUTFn LED Open Error FLAG

OUTGn, OUTHn LED Open Error FLAG

OUTAn, OUTBn Short-to-GND Error FLAG

OUTCn, OUTDn Short-to-GND Error FLAG

OUTEn, OUTFn Short-to-GND Error FLAG

OUTGn, OUTHn Short-to-GND Error FLAG

EEPROM Calculated CRC

Go

FLAG_SLS0

Go

FLAG_SLS1

Go

FLAG_SLS2

Go

FLAG_SLS3

Go

FLAG_OPEN0

FLAG_OPEN1

FLAG_OPEN2

FLAG_OPEN3

FLAG_SHORT0

FLAG_SHORT1

FLAG_SHORT2

FLAG_SHORT3

FLAG_EEPCRC

Go

Go

Go

Go

Go

Go

Go

Go

Go

Complex bit access types are encoded to fit into small table cells. 表 7-138 shows the codes that are used for

access types in this section.

表 7-138. FLAG Access Type Codes

Access Type

Read Type

R

Code

Description

R

Read

Reset or Default Value

-n

Value after reset or the default

value

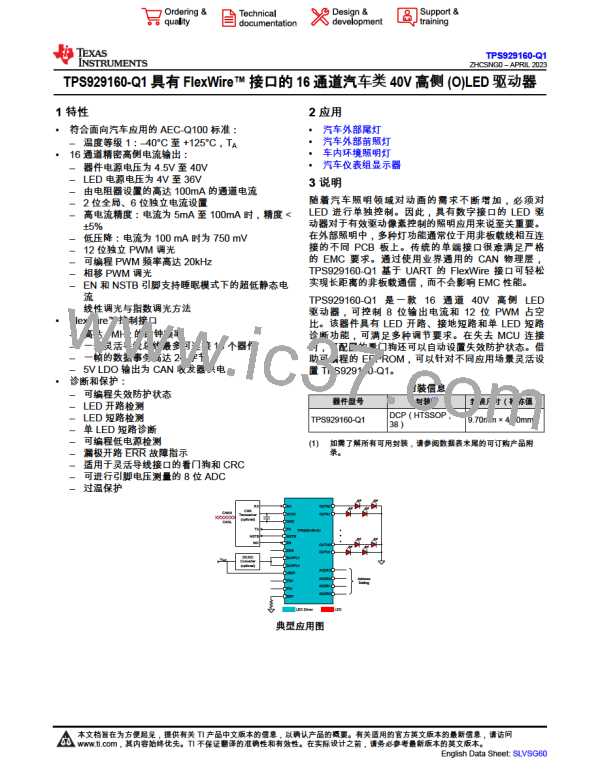

7.6.5.1 FLAG_ERR Register (Offset = A0h) [Reset = 01h]

FLAG_ERR is shown in 图 7-131 and described in 表 7-139.

Return to the Summary Table.

图 7-131. FLAG_ERR Register

7

6

5

4

3

2

1

0

FLAG_LOWSU FLAG_SUPUV

P

FLAG_REF

FLAG_PRETSD

FLAG_TSD

FLAG_EEPCR

C

FLAG_OUT

FLAG_ERR

R-0h

R-0h

R-0h

R-0h

R-0h

R-0h

R-0h

R-1h

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLVSG60

106 Submit Document Feedback

Product Folder Links: TPS929160-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]