TMP435

www.ti.com

SBOS495A –MARCH 2010–REVISED APRIL 2010

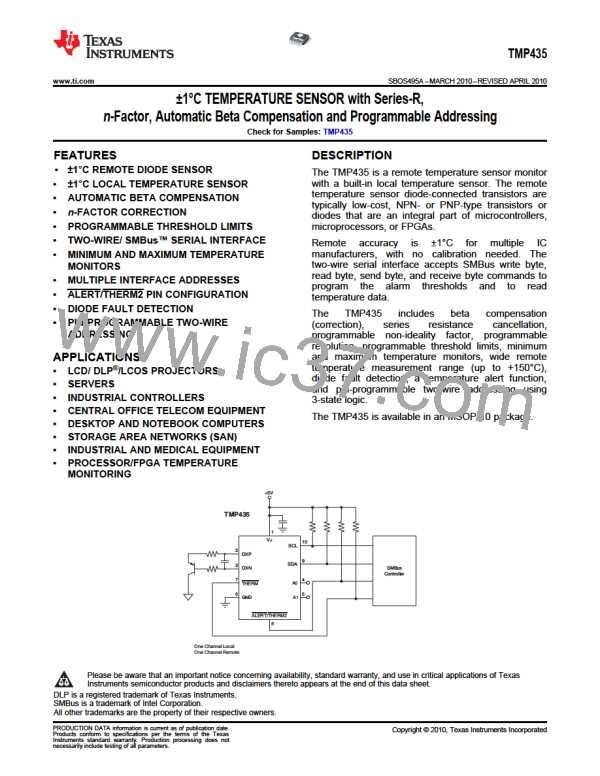

TIMING DIAGRAMS

Data Transfer: The number of data bytes transferred

between a START and a STOP condition is not

limited and is determined by the master device. The

receiver acknowledges the transfer of data.

The TMP435 is two-wire and SMBus-compatible.

Figure 15 to Figure 19 describe the various

operations on the TMP435. Bus definitions are given

below. Parameters for Figure 15 are defined in

Table 15.

Acknowledge: Each receiving device, when

addressed, is obliged to generate an Acknowledge

bit. A device that acknowledges must pull down the

SDA line during the Acknowledge clock pulse in such

a way that the SDA line is stable low during the high

period of the Acknowledge clock pulse. Setup and

hold times must be taken into account. On a master

receive, data transfer termination can be signaled by

the master generating a Not-Acknowledge on the last

byte that has been transmitted by the slave.

Bus Idle: Both SDA and SCL lines remain high.

Start Data Transfer: A change in the state of the

SDA line, from high to low, while the SCL line is high,

defines a START condition. Each data transfer is

initiated with a START condition.

Stop Data Transfer: A change in the state of the

SDA line from low to high while the SCL line is high

defines

a STOP condition. Each data transfer

terminates with a STOP or a repeated START

condition.

t(LOW)

tF

tR

t(HDSTA)

SCL

SDA

t(SUSTO)

t(HDSTA)

t(HIGH) t(SUSTA)

t(SUDAT)

t(HDDAT)

t(BUF)

P

S

S

P

Figure 15. Two-Wire Timing Diagram

Table 15. Timing Diagram Definitions for Figure 15

FAST MODE

HIGH-SPEED MODE

PARAMETER

MIN

MAX

MIN

MAX

UNITS

MHZ

ns

SCL Operating Frequency

f(SCL)

t(BUF)

0.001

0.4

0.001

3.4

Bus Free Time Between STOP

and START Condition

600

160

100

100

Hold time after repeated START

condition. After this period, the

first clock is generated.

t(HDSTA)

100

100

ns

ns

Repeated START Condition Setup

Time

t(SUSTA)

STOP Condition Setup Time

Data Hold Time

t(SUSTO)

t(HDDAT)

t(SUDAT)

t(LOW)

t(HIGH)

tF

100

0(1)

100

0(2)

10

ns

ns

ns

ns

ns

ns

ns

ns

Data Setup Time

100

1300

600

SCL Clock LOW Period

SCL Clock HIGH Period

Clock/Data Fall Time

Clock/Data Rise Time

for SCLK ≤ 100kHz

160

60

300

300

160

160

tR

1000

(1) For cases with fall time of SCL less than 20ns and/or the rise time or fall time of SDA less than 20ns, the hold time should be greater

than 20ns.

(2) For cases with fall time of SCL less than 10ns and/or the rise or fall time of SDA less than 10ns, the hold time should be greater than

10ns.

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

21

Product Folder Link(s): TMP435

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]