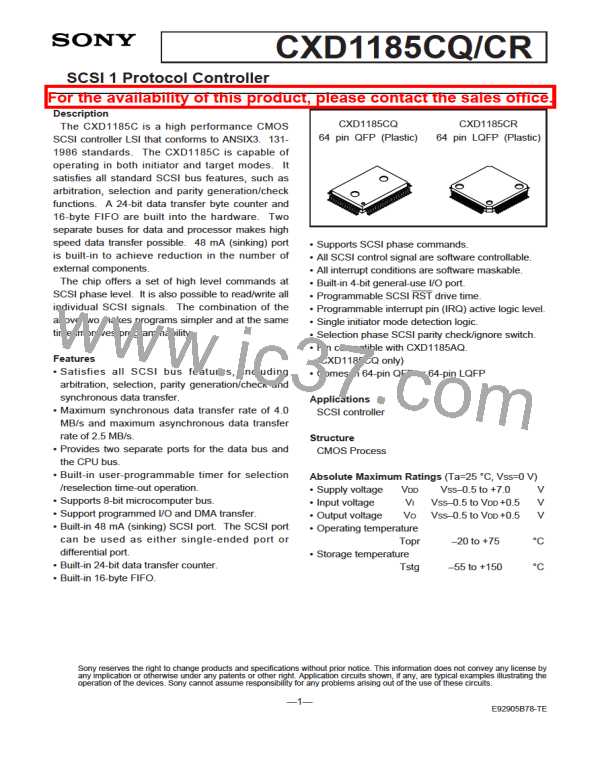

CXD1185CQ/CR

6. Programming Overview

The CXD1185C supports SCSI phase level commands. As a result, when it is operating it is possible to

perform programming without imposing a burden on the software. In this section actual methods for

programming the CXD1185C are introduced along with an explanation of all SCSI phases, assuming that

the CXD1185C is in the initiator mode and the target mode.

The below examples show cases where neither reselection phase nor sync transfer is performed.

6-1. Initiator mode

<Initial settings>

The CXD1185C is completely initialized when the power is turned on or after a hardware reset. Therefore,

the following initial settings must be performed.

1

2

Environment setting register initialization

The environment setting register is set to an initial value and initial clock division ratio of “4”. Therefore, a

new appropriate value must be written to match the external clock frequency as described in section 1-5.

If required, “1”s must be written to the other bits at the same time.

“Reset Chip” command execution

The new clock division ratio becomes valid only after executing the “Reset Chip” command. (The other

bits are valid as soon as they are written.) Therefore, if the clock division ratio is to be changed, the

“Reset Chip” command must be executed after changing the FSI and FSO bits in the environment setting

register.

3

“Enable Selection/Reselection” command execution

When either a “Hardware Reset” or “Reset Chip” command is executed, the selection/reselection

interrupts are disabled. An “Enable Selection/Reselection” command must be loaded in the command

register in order to accommodate selection/reselection interrupts.

<Arbitration/selection execution>

4

SCSI ID setting

The owner ID and target ID must be written to the SCSI ID register to prepare for selection.

5

Arbitration/selection

Write “1”s to some of the bits of interrupt authorization registers 1 and 2 (ARBF, STO, FNC, etc.) as

required. Write “Select with ATN” command into the command register. If message-out phase is not

necessary after selection, instead, write “Select without ATN” command. In this example “Select with

ATN” is assumed. Wait for the CIP bit in the status register to become “0” and read the interrupt request

registers.

If arbitration failed and ARBF bit is “1”, repeat 4. Normally, if selection time over occurs and STO bit set

to “1”, “Assert RST” command is executed.

<Message-out phase execution>

6

7

8

Switching to the message-out phase

Wait until the target device switches the SCSI bus to the message-out phase (PHC bit set to “1”).

Halting ATN signal drive

Execute “Deassert ATN” command to inactive the ATN signal on the SCSI bus.

Sending message byte

Confirm that the CIP bit is “0” in the status register. Write “Transfer Information” command to the

command register (DMA bit and TRBE bit are set to “0”s for a single byte message). Write the message

byte into the SCSI data register, After confirming that the CIP bit is to “0”, read interrupt request registers

1 and 2.

—27—

SONY [ SONY CORPORATION ]

SONY [ SONY CORPORATION ]