K9K1208Q0C

K9K1208D0C

K9K1208U0C

K9K1216Q0C

K9K1216D0C

K9K1216U0C

FLASH MEMORY

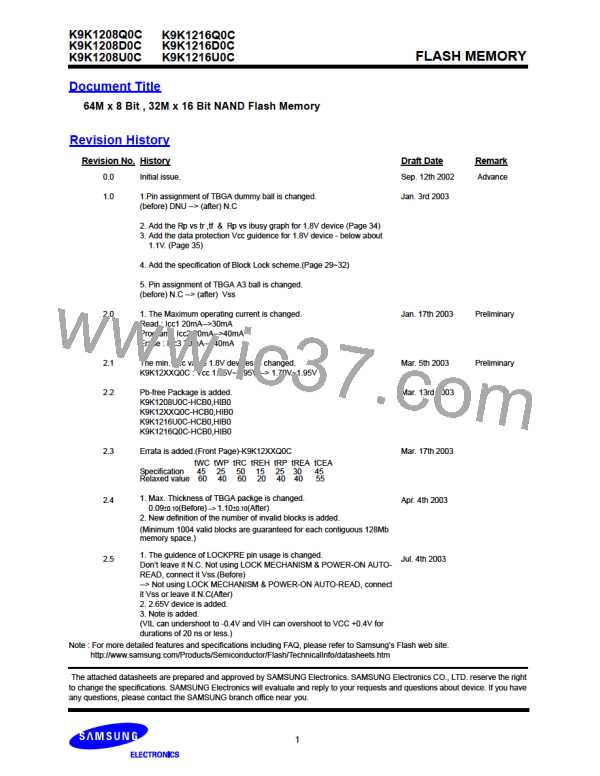

VALID BLOCK

Parameter

Symbol

Min

Typ.

Max

Unit

Valid Block Number

NVB

4026

-

4096

Blocks

NOTE :

1. The device may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is pre-

sented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or program

factory-marked bad blocks. Refer to the attached technical notes for a appropriate management of invalid blocks.

2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block, does not require Error Correction up to 1K program/erase

cycles.

3. Minimum 1004 valid blocks are guaranteed for each contiguous 128Mb memory space.

AC TEST CONDITION

(K9K12XXX0C-GCB0,JCB0 :TA=0 to 70°C, K9K12XXX0C-GIB0,JCB0 :TA=-40 to 85°C

K9K12XXQ0C : Vcc=1.70V~1.95V , K9K12XXD0C : Vcc=2.4V~2.9V , K9K12XXU0C : Vcc=2.7V~3.6V unless otherwise noted)

Parameter

K9K12XXQ0C

0V to VccQ

5ns

K9K12XXD0C

0V to VccQ

5ns

K9K12XXU0C

0.4V to 2.4V

5ns

Input Pulse Levels

Input Rise and Fall Times

Input and Output Timing Levels

VccQ/2

VccQ/2

1.5V

K9K12XXQ0C:Output Load (VccQ:1.8V +/-10%)

K9K12XXD0C:Output Load (VccQ:2.65V +/-10%) 1 TTL GATE and CL=30pF1 TTL GATE and CL=30pF 1 TTL GATE and CL=50pF

K9K12XXU0C:Output Load (VccQ:3.0V +/-10%)

K9K12XXU0C:Output Load (VccQ:3.3V +/-10%)

-

-

1 TTL GATE and CL=100pF

CAPACITANCE(TA=25°C, VCC=1.8V/2.65V/3.3V, f=1.0MHz)

Item

Symbol

Test Condition

Min

Max

Unit

pF

Input/Output Capacitance

Input Capacitance

CI/O

VIL=0V

-

-

20

20

CIN

VIN=0V

pF

NOTE : Capacitance is periodically sampled and not 100% tested.

MODE SELECTION

CLE

H

L

ALE

L

CE

L

WE

RE

H

LOCKPRE

WP

X

Mode

X

X

X

X

X

X

X

Command Input

Read Mode

Write Mode

H

L

L

H

X

Address Input(4clock)

Command Input

H

L

L

H

H

H

L

L

H

H

Address Input(4clock)

L

L

H

H

Data Input

L

L

L

H

X

X

Data Output

X

X

X

H

X

During Read(Busy) on the devices

X

X

X

X

X

X

X

X

X

H

X

X

X

X

X

X

X

X

X

X

X

H

During Program(Busy)

During Erase(Busy)

Write Protect

H

L

X(1)

X

(2

(2)

Stand-by

0V/VCC

0V/VCC

NOTE : 1. X can be VIL or VIH.

2. WP should be biased to CMOS high or CMOS low for standby.

11

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]