K7I163682B

K7I161882B

512Kx36 & 1Mx18 DDRII CIO b2 SRAM

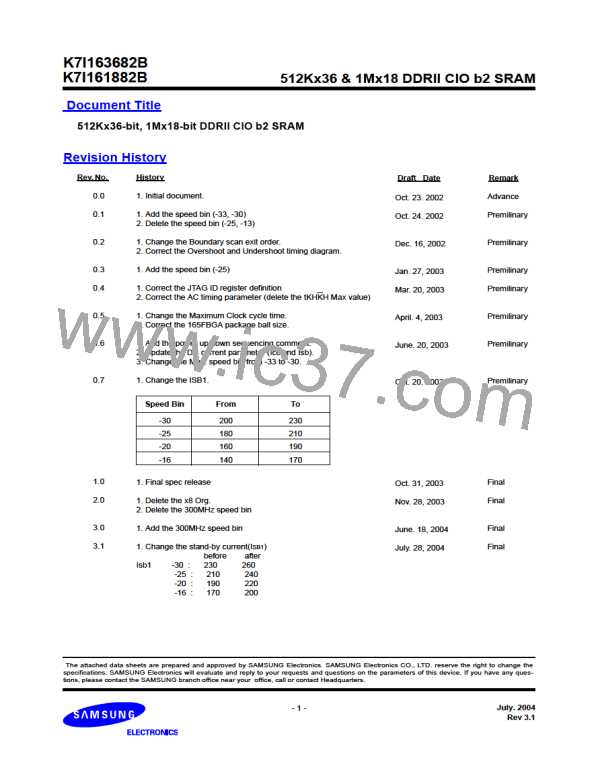

PIN CONFIGURATIONS(TOP VIEW) K7I161882B(1Mx18)

1

2

VSS/SA*

DQ9

NC

3

4

5

6

7

NC

BW0

SA

8

LD

SA

VSS

9

SA

10

Vss

NC

DQ7

NC

NC

NC

NC

VREF

DQ4

NC

NC

DQ1

NC

11

CQ

DQ8

NC

A

B

C

D

E

F

CQ

NC

NC

NC

NC

NC

NC

Doff

NC

NC

NC

NC

NC

NC

TDO

SA

NC

NC

R/W

SA

VSS

BW1

NC

SA

K

K

NC

NC

NC

NC

NC

NC

VDDQ

NC

NC

NC

NC

NC

NC

SA

SA0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SA

C

NC

NC

DQ12

NC

VREF

NC

NC

DQ15

NC

NC

NC

DQ10

DQ11

NC

DQ13

VDDQ

NC

DQ14

NC

NC

VSS

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VSS

VSS

SA

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VSS

VSS

SA

VSS

NC

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

DQ6

DQ5

NC

ZQ

NC

DQ3

DQ2

NC

NC

DQ0

TDI

G

H

J

K

L

M

N

P

R

DQ16

DQ17

SA

VSS

SA

SA

VSS

SA

SA

SA

SA

SA

SA

NC

TMS

TCK

C

Notes: 1. * Checked No Connect(NC) pins are reserved for higher density address, i.e. 2A for 72Mb.

2. BW0 controls write to DQ0:DQ8 and BW1 controls write to DQ9:DQ17.

PIN NAME

SYMBOL

K, K

PIN NUMBERS

DESCRIPTION

Input Clock

NOTE

6B, 6A

C, C

CQ, CQ

Doff

SA0

SA

6P, 6R

11A, 1A

1H

6C

Input Clock for Output Data

Output Echo Clock

DLL Disable when low

Burst Count Address Inputs

Address Inputs

1

3A,9A,4B,8B,5C,7C,5N-7N,4P,5P,7P,8P,3R-5R,7R-9R

2B,11B,10C,3D,3E,11E,2F,11F,3G,10J,3K,11K,2L,11L

10M,3N,3P,11P

DQ0-17

Data Inputs Outputs

Read, Write Control Pin, Read active

when high

R/W

4A

8A

Synchronous Load Pin, bus Cycle

sequence is to be defined when low

LD

BW0, BW1

VREF

7B, 5A

2H,10H

11H

Block Write Control Pin,active when low

Input Reference Voltage

Output Driver Impedance Control Input

Power Supply ( 1.8 V )

ZQ

VDD

2

5F,7F,5G,7G,5H,7H,5J,7J,5K,7K

VDDQ

VSS

4E,8E,4F,8F,4G,8G,3H,4H,8H,9H,4J,8J,4K,8K,4L,8L

Output Power Supply ( 1.5V or 1.8V )

Ground

2A,10A,4C,8C,4D-8D,5E-7E,6F,6G,6H,6J,6K,5L-7L,4M-8M,4N,8N

TMS

TDI

TCK

TDO

10R

11R

2R

JTAG Test Mode Select

JTAG Test Data Input

JTAG Test Clock

1R

JTAG Test Data Output

7A,1B,3B,5B,9B,10B,1C,2C,3C,9C,11C,1D,2D,9D,10D,11D

1E,2E,9E,10E,1F,3F,9F,10F,1G,2G,9G,10G,11G

1J,2J,3J,9J,11J,1K,2K,9K,10K,1L,3L,9L,10L

NC

No Connect

3

1M,2M,3M,9M,11M,1N,2N,9N,10N,11N,1P,2P,9P,10P

Notes: 1. C, C, K or K cannot be set to VREF voltage.

2. When ZQ pin is directly connected to VDD output impedance is set to minimum value and it cannot be connected to ground or left unconnected

3. Not connected to chip pad internally.

.

July. 2004

Rev 3.1

- 4 -

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]