FM24CL64B - 64Kb 3V I2C F-RAM (Automotive Temp.)

To perform a selective read, the bus master sends out

the slave address with the LSB set to 0. This specifies

a write operation. According to the write protocol,

the bus master then sends the address bytes that are

loaded into the internal address latch. After the

FM24CL64B acknowledges the address, the bus

master issues a start condition. This simultaneously

aborts the write operation and allows the read

command to be issued with the slave address LSB set

to a „1‟. The operation is now a current address read.

No

Acknowledge

Stop

Start

S

Address

By Master

By F-RAM

Slave Address

1

A

Data Byte

Data

1

P

Acknowledge

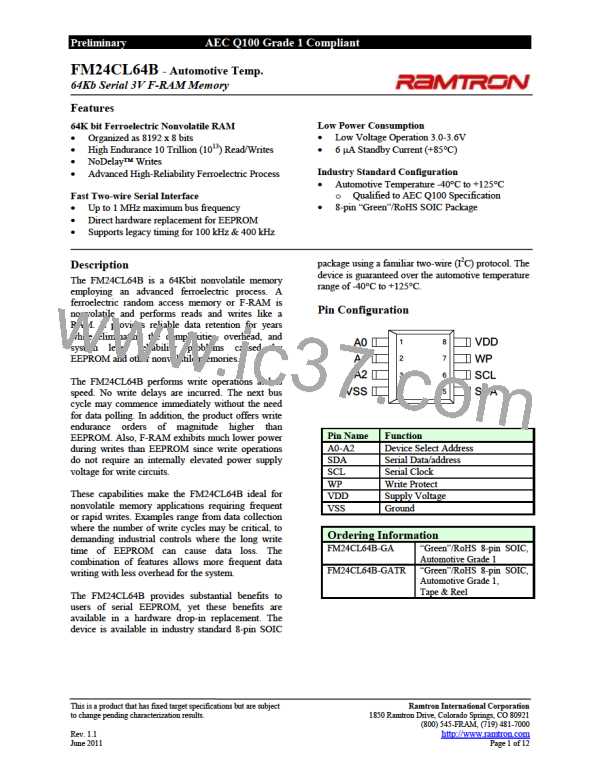

Figure 7. Current Address Read

No

Acknowledge

Start

S

Address

Acknowledge

By Master

By F-RAM

Stop

Slave Address

1

A

Data Byte

A

Data Byte

1

P

Acknowledge

Data

Figure 8. Sequential Read

Start

No

Address

Acknowledge

Start

Address

By Master

Stop

S

Slave Address

0

A

Address MSB

A

Address LSB

Acknowledge

A

S

Slave Address

1

A

Data Byte

Data

1 P

By F-RAM

Figure 9. Selective (Random) Read

Rev. 1.1

June 2011

Page 7 of 12

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]