®

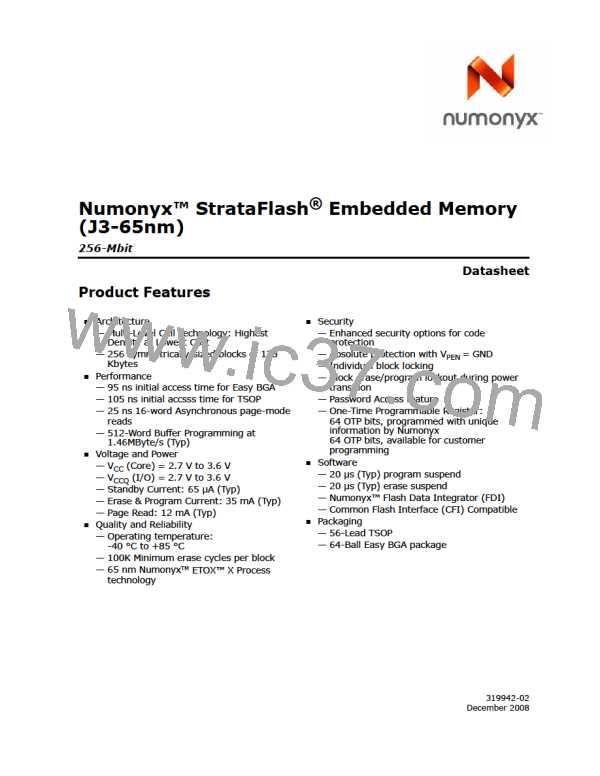

Numonyx™ StrataFlash Embedded Memory (J3-65nm)

10.0

Security

J3-65nm device offer both hardware and software security features. Block lock

operations, PRs and VPEN allow users to implement various levels of data protection.

10.1

Normal Block Locking

J3-65nm has the unique capability of Flexible Block Locking (locked blocks remain

locked upon reset or power cycle): All blocks are unlocked at Numonyx factory. Blocks

can be locked individually by issuing the Set Block Lock Bit command sequence to any

address within a block. Once locked, blocks remain locked when power is removed, or

when the device is reset (see Figure 20, “Block Lock Operations Flowchart” on

page 60).

All locked blocks are unlocked simultaneously by issuing the Clear Block Lock Bits

command sequence to any device address. Locked blocks cannot be erased or

programmed. Table 8 summarizes the command bus-cycles.

After issuing the Set Block Lock Bit setup command or Clear Block Lock Bits setup

command, the device’s read mode is automatically changed to Read Status Register

mode. After issuing the confirm command, completion of the operation is indicated by

STS (in RY/BY# mode) going high and SR.7 = 1.

Blocks cannot be locked or unlocked while programming or erasing, or while the device

is suspended. Reliable block lock and unlock operations occur only when VCC and VPEN

are valid. When VPEN ≤ VPENLK, block lock-bits cannot be changed.

When the set lock-bit operation is complete, SR.4 should be checked for any error.

When the clear lock-bit operation is complete, SR.5 should be checked for any error.

Errors bits must be cleared using the Clear Status Register command.

Block lock-bit status can be determined by first issuing the Read Device Information

command, and then reading from <block base address> + 02h. DQ0 indicates the lock

status of the addressed block (0 = unlocked, 1 = locked).

10.2

Configurable Block Locking

One of the unique new features on the J3-65nm,which did not exist on the previous

generations of this product family, is the ability to protect and/or secure the user’s

system by offering multiple level of securities: Non-Volatile Temporary; Non-Volatile

Semi-Permanent or Non-Volatile Permanent. For additional information and collateral

request, please contact your filed representative .

Datasheet

28

December 2008

319942-02

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]