®

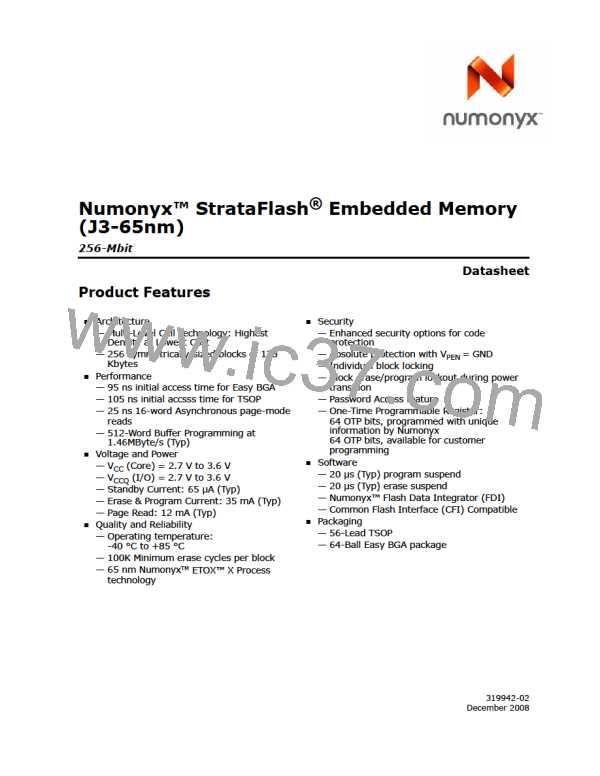

Numonyx™ StrataFlash Embedded Memory (J3-65nm)

8.0

Program operation

All programming operations require the addressed block to be unlocked, and a valid

VPEN voltage applied throughout the programming operation. Otherwise, the

programming operation will abort, setting the appropriate Status Register error bit(s).

The following sections describe each programming method.

8.1

Single-Word/Byte Programming

Array programming is performed by first issuing the Single-Word/Byte Program

command. This is followed by writing the desired data at the desired array address. The

read mode of the device is automatically changed to Read Status Register mode, which

remains in effect until another read-mode command is issued.

During programming, STS and the Status Register indicate a busy status (SR.7 = 0).

Upon completion, STS and the Status Register indicate a ready status (SR.7 = 1). The

Status Register should be checked for any errors (SR.4), then cleared.

Note:

Issuing the Read Array command to the device while it is actively programming causes

subsequent reads from the device to output invalid data. Valid array data is output only

after the program operation has finished.

Standby power levels are not realized until the programming operation has finished.

Also, asserting RP# aborts the programming operation, and array contents at the

addressed location are indeterminate. The addressed block should be erased, and the

data re-programmed. If a Single-Word/Byte program is attempted when the

corresponding block lock-bit is set, SR.1 and SR.4 will be set.

8.2

Buffered Programming

The device features a 512-word buffer to enable optimum programming performance.

For Buffered Programming, data is first written to an on-chip write buffer. Then the

buffer data is programmed into the flash memory array in buffer-size increments. This

can improve system programming performance significantly over non-buffered

programming. (see Figure 19, “Buffer Program Flowchart” on page 59).

When the Buffered Programming Setup command is issued, Status Register information

is updated and reflects the availability of the buffer. SR.7 indicates buffer availability: if

set, the buffer is available; if cleared, the buffer is not available. To retry, issue the

Buffered Programming Setup command again, and re-check SR.7. When SR.7 is set,

the buffer is ready for loading.

On the next write, a word count is written to the device at the buffer address. This tells

the device how many data words will be written to the buffer, up to the maximum size

of the buffer.

On the next write, a device start address is given along with the first data to be written

to the flash memory array. Subsequent writes provide additional device addresses and

data. All data addresses must lie within the start address plus the word count.

Optimum programming performance and lower power usage are obtained by aligning

the starting address at the beginning of a 512-word boundary (A[9:1] = 0x00). The

maximum buffer size would be 256-word if the misaligned address range is crossing a

512-word boundary during programming.

After the last data is written to the buffer, the Buffered Programming Confirm command

must be issued to the original block address. The WSM begins to program buffer

contents to the flash memory array. If a command other than the Buffered

Datasheet

24

December 2008

319942-02

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]