®

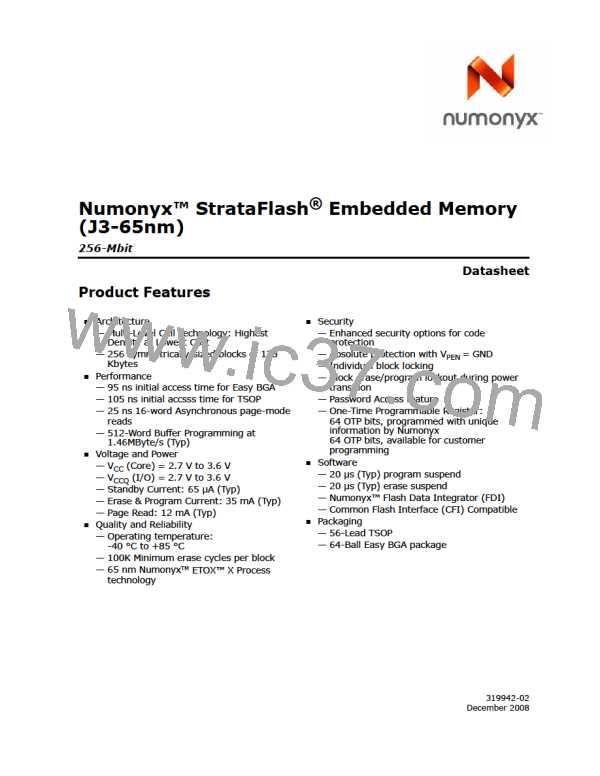

Numonyx™ StrataFlash Embedded Memory (J3-65nm)

11.0

Registers

11.1

Status Register

The Status Register (SR) is an 8-bit, read-only register that indicates device status and

operation errors. To read the Status Register, issue the Read Status Register command.

Subsequent reads output Status Register information on DQ[7:0], and 00h on

DQ[15:8].

SR status bits are set and cleared by the device. SR error bits are set by the device, but

must be cleared using the Clear Status Register command. Upon power-up or exit from

reset, the Status Register defaults to 80h. Page-mode reads are not supported in this

read mode. Status Register contents are latched on the falling edge of OE# or the first

edge of CEx that enables the device. OE# must toggle to VIH or the device must be

disabled before further reads to update the Status Register latch. The Read Status

Register command functions independently of VPEN voltage.

Table 11 shows Status Register bit definitions.

Table 11: Status Register Description

Status Register (SR)

Default Value = 0x80

Program

Suspend

Status

Device Write

Status

Erase Suspend

Status

Program

Status

Prog/Erase

Block-Locked

Erase Status

Reserved

0

Voltage Error

Status

DWS

7

ESS

6

ES

5

PS

4

PEVE

3

PSS

2

BLS

1

Bit

Name

Description

0 = Device is busy; program or erase cycle in progress.

1 = Device is ready; SR[6:1] are valid.

7

6

5

4

3

2

Device Write Status (DWS)

Erase Suspend Status (ESS)

Erase Status (ES)

0 = Erase suspend not in effect.

1 = Erase suspend in effect.

0 = Erase successful.

1 = Erase fail or program sequence error when set with SR.4,SR.7.

0 = Program successful.

1 = Program fail or program sequence error when set with SR.5,SR.7

Program Status (PS)

0 = VPEN within acceptable limits during program or erase operation.

Prog/Erase Voltage Error (PEVE)

Program Suspend Status (PSS)

1 = VPEN ≤ V

during program or erase operation.

PENLK

0 = Program suspend not in effect.

1 = Program suspend in effect.

0 = Block not locked during program or erase.

1 = Block locked during program or erase; operation aborted.

1

0

Block-Locked Status (BLS)

Reserved

0 = Default

Note: Always clear the Status Register prior to resuming erase operations. It avoids Status Register ambiguity when issuing

commands during Erase Suspend. If a command sequence error occurs during an erase-suspend state, the Status

Register contains the command sequence error status (SR[7,5,4] set). When the erase operation resumes and finishes,

possible errors during the erase operation cannot be detected via the Status Register because it contains the previous

error status

Datasheet

30

December 2008

319942-02

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]