®

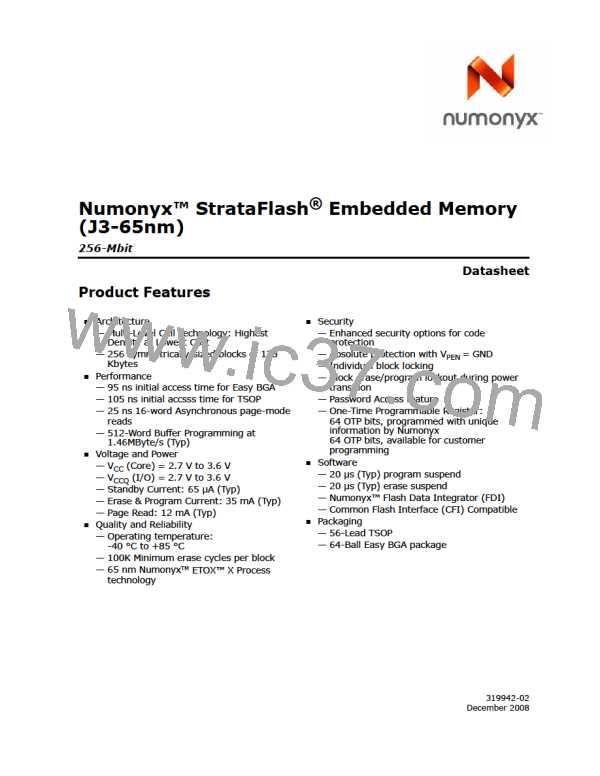

Numonyx™ StrataFlash Embedded Memory (J3-65nm)

5.5

Reset

RP# at VIL initiates the reset/power-down mode.

In read modes, RP#-low deselects the memory, places output drivers in a high-

impedance state, and turns off numerous internal circuits. RP# must be held low for a

minimum of tPLPH. Time tPHQV is required after return from reset mode until initial

memory access outputs are valid. After this wake-up interval, normal operation is

restored. The CUI is reset to read array mode and Status Register is set to 0080h.

During Block Erase, Program, or Lock-Bit Configuration modes, RP#-low will abort the

operation. In default mode, STS transitions low and remains low for a maximum time

of tPLPH + tPHRH until the reset operation is complete. Memory contents being altered

are no longer valid; the data may be partially corrupted after a program or partially

altered after an erase or lock-bit configuration. Time tPHWL is required after RP# goes to

logic-high (VIH) before another command can be written.

As with any automated device, it is important to assert RP# during system reset. When

the system comes out of reset, it expects to read from the flash memory. Automated

flash memories provide status information when accessed during Block Erase, Program,

or Lock-Bit Configuration modes. If a CPU reset occurs with no flash memory reset,

proper initialization may not occur because the flash memory may be providing status

information instead of array data. Numonyx Flash memories allow proper initialization

following a system reset through the use of the RP# input. In this application, RP# is

controlled by the same RESET# signal that resets the system CPU.

December 2008

319942-02

Datasheet

17

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]