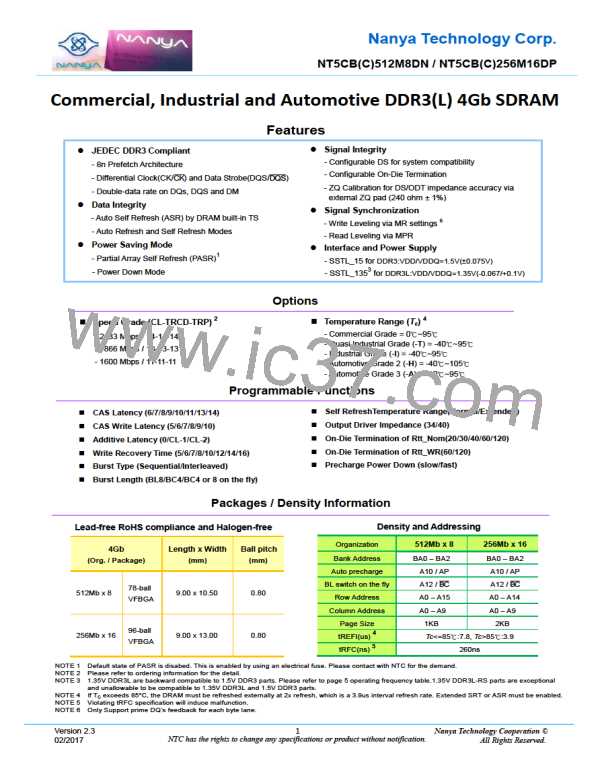

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

CAS Write Latency (CWL)

The CAS Write Latency is defined by MR2 (bits A3-A5) shown in MR2. CAS Write Latency is the delay, in clock cycles,

between the internal Write command and the availability of the first bit of input data. DDR3(L) DRAM does not support any

half clock latencies. The overall Write Latency (WL) is defined as Additive Latency (AL) + CAS Write Latency (CWL);

WL=AL+CWL.

Auto Self-Refresh (ASR) and Self-Refresh Temperature (SRT)

DDR3(L) SDRAM must support Self-Refresh operation at all supported temperatures. Applications requiring Self-Refresh

operation in the Extended Temperature Range must use the ASR function or program the SRT bit appropriately.

Optional in DDR3(L) SDRAM: Users should refer to the DRAM supplier data sheet and/or the DIMM SPD to determine if

DDR3(L) SDRAM devices support the following options or requirements referred to in this material. For more details refer to

“Extended Temperature Usage”. DDR3(L) SDRAMs must support Self-Refresh operation at all supported temperatures.

Applications requiring Self-Refresh operation in the Extended Temperature Range must use the optional ASR function or

program the SRT bit appropriately.

Dynamic ODT (Rtt_WR)

DDR3(L) SDRAM introduces a new feature “Dynamic ODT”. In certain application cases and to further enhance signal

integrity on the data bus, it is desirable that the termination strength of the DDR3(L) SDRAM can be changed without

issuing an MRS command. MR2 Register locations A9 and A10 configure the Dynamic ODT settings. In Write leveling

mode, only RTT_Nom is available. For details on Dynamic ODT operation, refer to “Dynamic ODT”.

Version 2.3

02/2017

26

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]