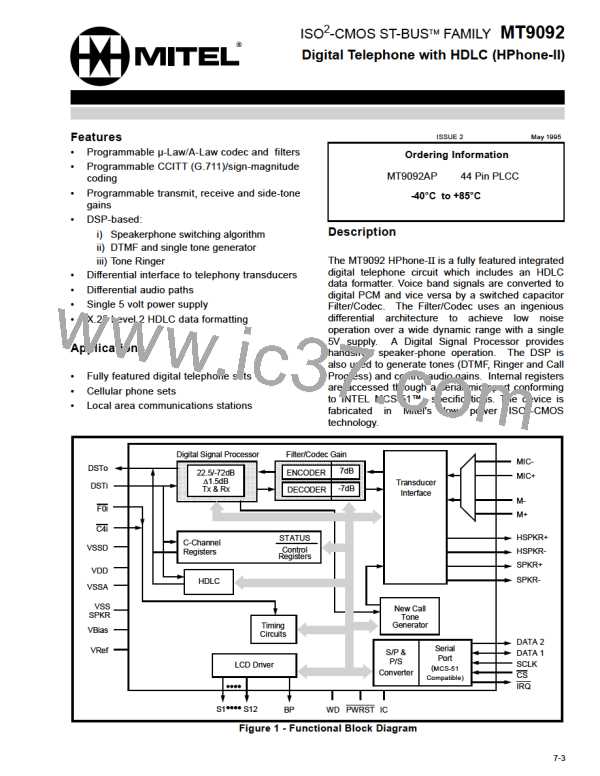

MT9092

The data streams operate at 2048kb/s and are Time

Division Multiplexed into 32 identical channels of

64kb/s bandwidth. Frame Pulse (a 244nSec low

going pulse) is used to parse the continuous serial

data streams into the 32 channel TDM frames. Each

frame has a 125µSecond period translating into an 8

kHz frame rate. Valid frame pulse occurs when F0i is

logic low coincident with a falling edge of C4i. C4i

has a frequency (4096MHz) which is twice the data

rate. This clock is used to sample the data at the 3/4

bit-cell position on DSTi and to make data available

on DSTo at the start of the bit-cell. C4i is also used

to clock the HPhone-II internal functions (i.e., DSP,

Filter/CODEC, HDLC) and to provide the channel

timing requirements.

Ch EN - C-Channel

1

Channel

1

conveys

the

control/status

information for Mitel’s layer 1 transceiver. The

full 64kb/s bandwidth is available and is

assigned according to which transceiver is

being used. Consult the data sheet for the

selected transceiver for its bit definitions and

order of bit transfer. When this bit is high

register data is transmitted on DSTo. When low,

this timeslot is tri-stated on DSTo. Receive C-

Channel data (DSTi) is always routed to the

register regardless of this control bit's logic

state. C-channel data is transferred on the ST-

BUS MSB first by the HPhone-II.

Ch EN and Ch EN - B1-Channel and B2-Channel

2

3

The HPhone-II uses only the first 4 channels of the

32 channel frame. These channels are always

defined, beginning with the first channel after frame

pulse, as shown in Figure 7 (DSTi and DSTo channel

assignments). Channels are enabled independantly

Channels 2 and 3 are the B1 and B2 channels,

respectively. These bits (Ch EN and Ch EN)

2

3

are used to enable the PCM channels from/to

the HPhone-II as required.

by the four control bits Ch En -Ch En residing in the

Timing Control Register (address15h).

0

3

Transmit PCM on DSTo

When high, PCM from the Filter/CODEC and DSP is

transmitted on DSTo in the selected ST-BUS

channel. When low, DSTo is forced to logic 0 for the

Ch EN - D-Channel

0

Channel 0 conveys the D-Channel HDLC

information. Since this function is dedicated to

16kb/s operation, only the first two bits (LSB's)

of the octet are required; the remaining six bits

of the D-Channel octet carry no information and

corresponding timeslot. If both Ch EN and Ch EN

2

3

are enabled, default is to channel 2.

Receive PCM from DSTi

are tri-stated. When CH EN is high, HDLC data

0

is transmitted on DSTo. When low, DSTo is

forced to logic 0 for the two least significant bit

When high, PCM from DSTi is routed to the DSP and

Filter/CODEC in the associated channel. If both

positions.

Incoming DSTi data is always

routed to the HDLC block regardless of this

control bit's logic state.

Ch EN and Ch EN are enabled the default is to

2

3

channel 2.

125 µs

F0i

CHANNEL 0 CHANNEL 1 CHANNEL 2

CHANNEL 3

B2-channel

CHANNELS 4 - 31

Not Used

DSTi,

DSTo

D-channel

C-channel

B1-channel

LSB first

for D-

Channel

MSB first for C, B1 - & B2-

Channels

Figure 7 - ST-BUS Channel Assignment

7-19

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]