Preliminary Information

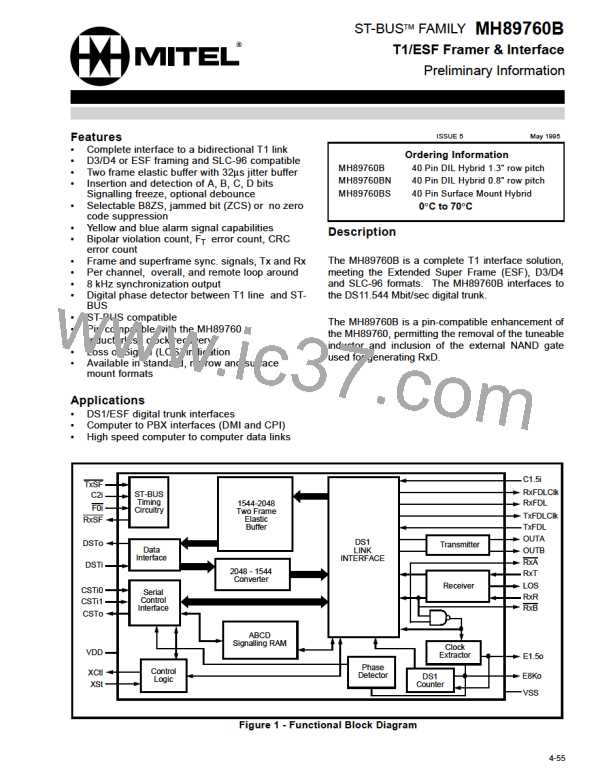

MH89760B

Control and monitoring of the T1 interface is done

through the MT8980 switch matrix. CSTi0 and

CSTo1 are connected to the ST-BUS streams that

are configured for message mode so the controlling

microprocessor can access the Master Control

Words and the Master Status Words.

systems is the ST-BUS. Therefore, a T1 to CEPT

digital trunk converter can be realized.

Figure 18 shows five blocks which are the T1

interface, switch matrix, CEPT interface, clock

generation and synchronization, and DSP Element.

The T1 interface converts the 1.544 MHz serial

stream into the ST-BUS format which interfaces to

the switch matrix through DSTi and DSTo. The CEPT

interface converts the 2.048 MHz serial stream into

the ST-BUS format and interfaces to the switch

matrix through the DSP element.

The received portion of the T1 interface extracts the

data from the T1 stream and formats it into ST-BUS

channels. The MT8980 switches these ST-BUS

channels into the first 24 consecutive channels of an

ST-BUS stream, which is passed to the protocol

conversion block. HDLC packets are disassembled

from the incoming ST-BUS stream by the MT8952.

With both the T1 data and the CEPT data converted

to the ST-BUS format, the two digital trunks can

exchange information through the switch matrix.

Unfortunately, the signalling information from the two

formats is not exchanged as easily. The T1 A and B

signalling bits must be read by the controlling

microprocessor and converted in software to the

CEPT ABCD signalling bits, and vice versa. The

circuit must also convert all the channels carrying

voice data to the appropriate encoding scheme, (i.e.,

T1 µ-Law or CEPT A-Law). This is done by the block

labelled DSP in Figure 18, Digital Signal Processor.

Clock generation and synchronization are handled

by the MT8941. DPLL #2 generates ST-BUS clocks

that are phase-locked to the extracted 8KHz, and

DPLL #1 generates the transmit T1 clock that is

phase-locked to the ST-BUS frame pulse. Therefore,

the interface is operating in a loop timed mode and

there will be no loss of information due to slips. The

MT8941 can also be configured to operate in a

master timing mode.

8. T1 to CEPT Digital Trunk Converter

The final component of the system is the MT8941.

The extracted 8 kHz outputs from the T1 and the

CEPT interfaces are combined with an AND gate

before being connected to the MT8941. One of the

The two main digital trunk transmission formats in

use today are T1 and CEPT. Mitel's T1 and CEPT

interfaces convert the digital trunk format into ST-

BUS format. The common element between the two

CEPT Interface

MH89790B

Switch Matrix

MT8980

T1 Interface

MH89760B

DSP

RxT

RxA

Element

DSTi

DSTo

DSTi

DSTo

CSTo

STi0

STo0

STo1

STi1

RxR

RxB

CSTi0

STo3

STi2

STo4

STi4

STo2

STo3

CSTi1

CSTo

CSTi0

CSTi1

OUTA

OUTB

OUTA

OUTB

C4i

F0i

C2i

F0i

F0i

C2i

C1.5i

E8Ko

µP

E8Ko

MT8941

DPLL #1

C1.5o

DPLL #2

F0o

C2o

E8Ki

C4o

Clock Generator

Figure 18 - T1 to CEPT Digital Trunk Converter

4-79

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]