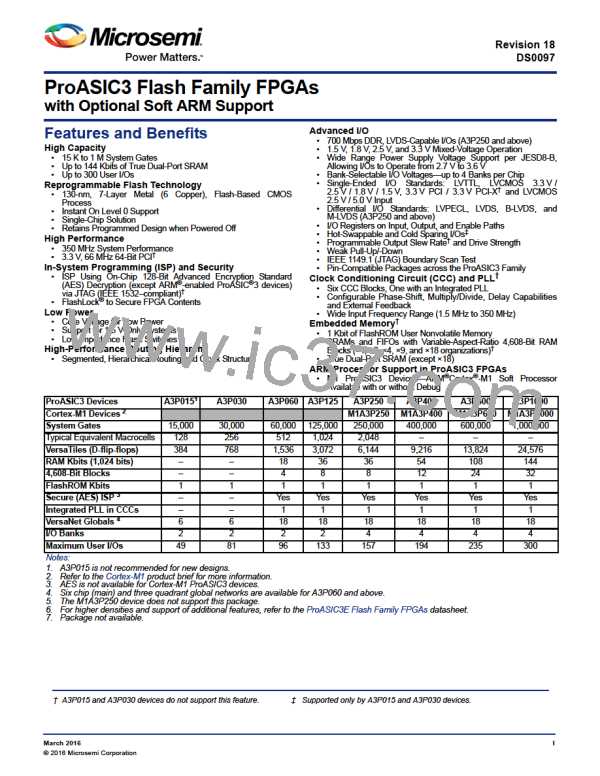

ProASIC3 Flash Family FPGAs

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device

provides the best available security for programmable logic designs.

Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration

data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-

up (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration

components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials

costs and PCB area, and increases security and system reliability.

Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system

component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory

blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices

greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock

generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will

not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be

reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM,

expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based

ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and

improving system initialization time.

Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a

configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and

thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in

SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the

configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of

ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft)

errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and

correction (EDAC) circuitry built into the FPGA fabric.

Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for

power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current

transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

Revision 18

1-2

MICROSEMI [ Microsemi ]

MICROSEMI [ Microsemi ]