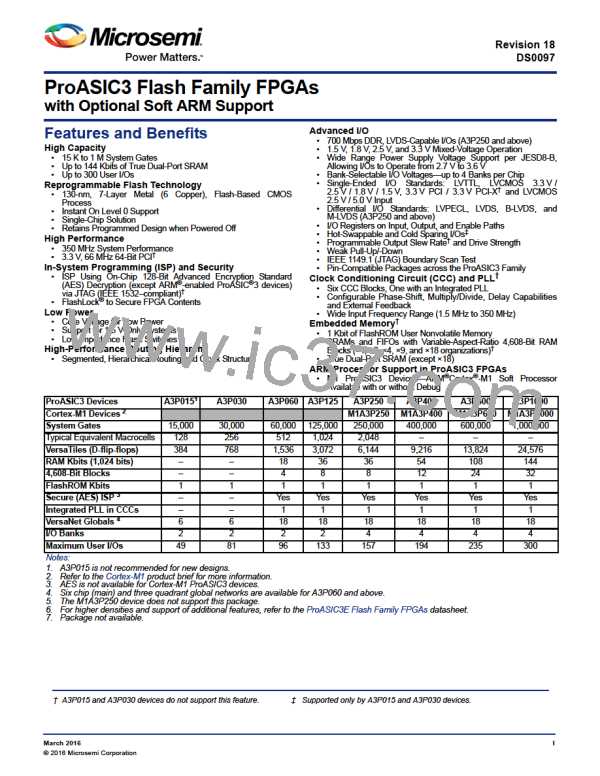

ProASIC3 Flash Family FPGAs

1

I/Os Per Package

ProASIC3

Devices

A3P0152 A3P030 A3P060 A3P125

A3P250 3

A3P400 3

A3P600

A3P1000

Cortex-M1

Devices

M1A3P250 3,5

I/O Type

M1A3P400 3

M1A3P600

M1A3P1000

Package

QN48

–

49

–

34

49

81

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

QN68

–

–

–

–

QN1327

CS121

VQ100

TQ144

PQ208

FG144

FG2565,6

FG4846

Notes:

80

96

71

91

–

84

–

87

–

19

–

–

–

–

–

–

–

–

–

–

–

77

–

71

100

133

97

–

68

–

13

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

151

97

157

–

34

24

38

–

151

97

178

194

34

25

38

38

154

97

35

25

43

60

154

97

177

300

35

25

44

74

–

–

96

–

–

–

177

235

–

–

–

–

1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3 FPGA Fabric User Guide to

ensure complying with design and board migration requirements.

2. A3P015 is not recommended for new designs.

3. For A3P250 and A3P400 devices, the maximum number of LVPECL pairs in east and west banks cannot exceed 15. Refer to

the ProASIC3 FPGA Fabric Users Guide for position assignments of the 15 LVPECL pairs.

4. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

5. The M1A3P250 device does not support FG256 package.

6. FG256 and FG484 are footprint-compatible packages.

7. Package not available.

Table 1 • ProASIC3 FPGAs Package Sizes Dimensions

Package

CS121

QN48

QN68

QN132 * VQ100

TQ144

PQ208

FG144

FG256

FG484

Length × Width

(mm × mm)

6 × 6

6 × 6

8 × 8

8 × 8

14 × 14

20 × 20

28 × 28

13 × 13

17 × 17

23 × 23

Nominal Area

(mm2)

36

36

64

64

196

400

784

169

289

529

Pitch (mm)

0.5

0.4

0.4

0.5

0.5

0.5

0.5

1.0

1.0

1.0

Height (mm)

0.99

0.90

0.90

0.75

1.00

1.40

3.40

1.45

1.60

2.23

Note: * Package not available

Revision 18

III

MICROSEMI [ Microsemi ]

MICROSEMI [ Microsemi ]