ADVANCE

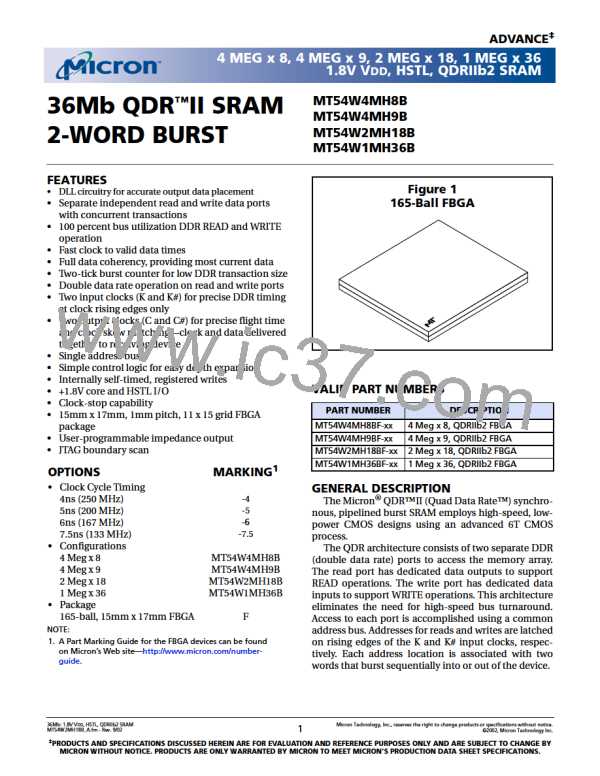

4 MEG x 8, 4 MEG x 9, 2 MEG x 18, 1 MEG x 36

1.8V VDD, HSTL, QDRIIb2 SRAM

BOUNDARY SCAN (EXIT) ORDER

BIT#

FBGA BALL

BIT#

FBGA BALL

BIT#

FBGA BALL

1

6R

6P

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

10D

9E

73

74

2C

3E

2

3

6N

10C

11D

9C

75

2D

2E

4

7P

76

5

7N

77

1E

6

7R

9D

11B

11C

9B

78

2F

7

8R

79

3F

8

8P

80

1G

1F

9

9R

81

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

11P

10P

10N

9P

10B

11A

10A

9A

8B

82

3G

2G

1H

1J

83

84

85

10M

11N

9M

9N

86

2J

7C

87

3K

3J

6C

88

8A

7A

7B

89

2K

1K

2L

11L

11M

9L

90

91

6B

92

3L

10L

11K

10K

9J

6A

5B

93

1M

1L

94

5A

4A

5C

95

3N

3M

1N

2M

3P

96

9K

97

10J

11J

11H

10G

9G

4B

98

3A

2A

1A

2B

99

100

101

102

103

104

105

106

107

108

109

2N

2P

1P

11F

11G

9F

3B

3R

1C

4R

1B

4P

10F

11E

10E

3D

3C

5P

5N

5R

1D

INTERNAL

NOTE:

For NC balls in the range of 1B-1P, 2B-2P, 3B-3P, 9B-9P, 10B-10P, and 11B-11P, a logic zero will be read from the chain. All other

NC balls will appear in the scan chain as the logic level present on the ball site.

36Mb: 1.8V VDD, HSTL, QDRIIb2 SRAM

MT54W2MH18B_A.fm - Rev 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

25

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]