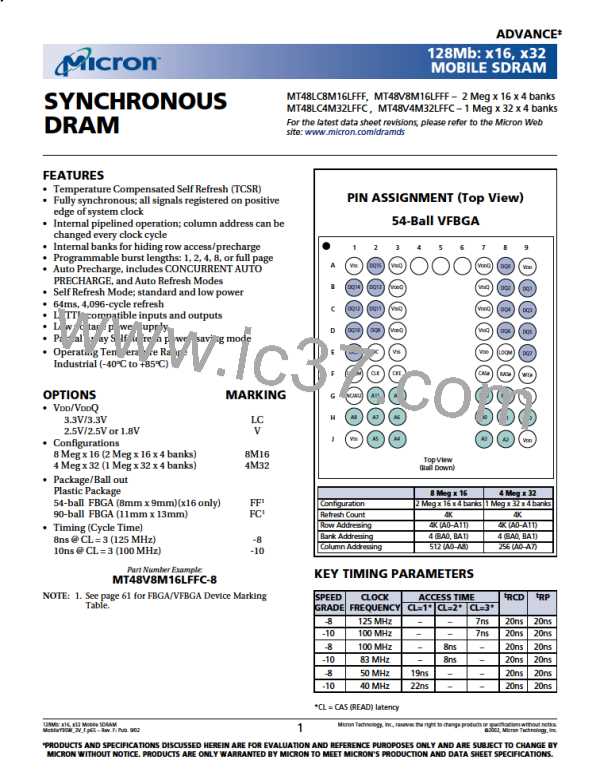

ADVANCE

128Mb: x16, x32

MOBILE SDRAM

PRECHARGE command is that it requires that the com-

mand and address buses be available at the appropriate

time to issue the command; the advantage of the

PRECHARGE command is that it can be used to truncate

fixed-length or full-page bursts.

Full-page READ bursts can be truncated with the

BURST TERMINATE command, and fixed-length READ

burstsmaybetruncatedwithaBURSTTERMINATEcom-

mand, provided that auto precharge was not activated.

The BURST TERMINATE command should be issued x

cycles before the clock edge at which the last desired data

element is valid, where x equals the CAS latency minus

one. This is shown in Figure 12 for each possible CAS

latency; data element n + 3 is the last desired data ele-

ment of a longer burst.

Figure 12

Terminating a READ Burst

T0

T1

T2

T3

T4

T5

T6

CLK

BURST

TERMINATE

READ

NOP

NOP

NOP

NOP

NOP

COMMAND

ADDRESS

DQ

X = 0 cycles

BANK,

COL n

D

OUT

D

n + 1

OUT

D

n + 2

OUT

DOUT

n

n + 3

CAS Latency = 1

T0

T1

T2

T3

T4

T5

T6

CLK

BURST

TERMINATE

READ

NOP

NOP

NOP

NOP

NOP

COMMAND

ADDRESS

DQ

X = 1 cycle

BANK,

COL n

D

OUT

D

n + 1

OUT

DOUT

D

n + 3

OUT

n

n + 2

CAS Latency = 2

T1

T0

T2

T3

T4

T5

T6

T7

CLK

COMMAND

ADDRESS

DQ

BURST

TERMINATE

READ

NOP

NOP

NOP

NOP

NOP

NOP

X = 2 cycles

BANK,

COL n

D

OUT

DOUT

D

n + 2

OUT

D

n + 3

OUT

n

n + 1

CAS Latency = 3

NOTE: DQM is LOW.

DON’T CARE

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

23

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]