ADVANCE

128Mb: x16, x32

MOBILE SDRAM

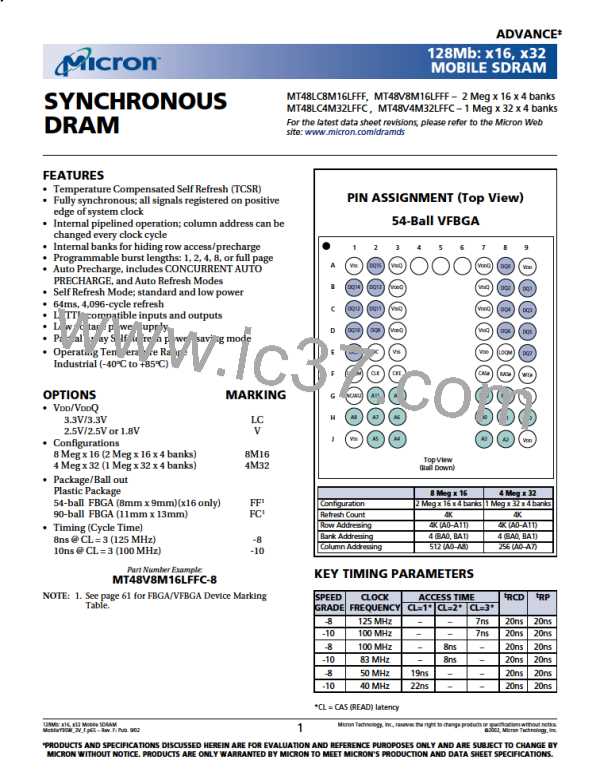

Figure 8

Random READ Accesses

T0

T1

T2

T3

T4

CLK

COMMAND

ADDRESS

DQ

READ

READ

READ

READ

NOP

BANK,

COL n

BANK,

COL a

BANK,

COL x

BANK,

COL m

DOUT

DOUT

D

OUT

D

OUT

n

a

x

m

CAS Latency = 1

T0

T1

T2

T3

T4

T5

CLK

COMMAND

ADDRESS

DQ

READ

READ

READ

READ

NOP

NOP

BANK,

COL n

BANK,

COL a

BANK,

COL x

BANK,

COL m

DOUT

DOUT

D

OUT

D

OUT

n

a

x

m

CAS Latency = 2

T0

T1

T2

T3

T4

T5

T6

CLK

READ

READ

READ

READ

NOP

NOP

NOP

COMMAND

ADDRESS

DQ

BANK,

COL n

BANK,

COL a

BANK,

COL x

BANK,

COL m

DOUT

D

OUT

D

OUT

D

OUT

n

a

x

m

CAS Latency = 3

NOTE: Each READ command may be to either bank. DQM is LOW.

DON’T CARE

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

20

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]