ADVANCE

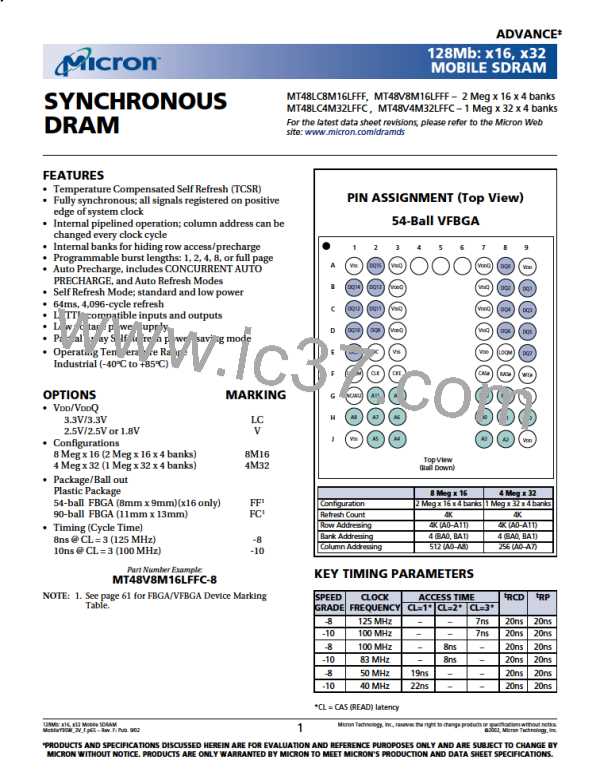

128Mb: x16, x32

MOBILE SDRAM

SELF REFRESH

AUTO REFRESH

The SELF REFRESH command can be used to retain

data in the SDRAM, even if the rest of the system is

powereddown.Whenintheselfrefreshmode,theSDRAM

retains data without external clocking. The SELF RE-

FRESH command is initiated like an AUTO REFRESH

command except CKE is disabled (LOW). Once the SELF

REFRESH command is registered, all the inputs to the

SDRAM become “Don’t Care” with the exception of CKE,

which must remain LOW.

AUTO REFRESH is used during normal operation of

the SDRAM and is analogous to CAS#-BEFORE-RAS#

(CBR) REFRESH in conventional DRAMs. This

command is nonpersistent, so it must be issued each

time a refresh is required. All active banks must be

PRECHARGED prior to issuing an AUTO REFRESH

command. The AUTO REFRESH command should not

be issued until the minimum RP has been met after the

PRECHARGE command as shown in the operation sec-

tion.

t

Once self refresh mode is engaged, the SDRAM pro-

vides its own internal clocking, causing it to perform its

own AUTO REFRESH cycles. The SDRAM must remain in

The addressing is generated by the internal refresh

controller. This makes the address bits “Don’t Care”

duringanAUTOREFRESHcommand.The128MbSDRAM

t

self refresh mode for a minimum period equal to RAS

t

and may remain in self refresh mode for an indefinite

period beyond that.

requires 4,096 AUTO REFRESH cycles every 64ms ( REF),

regardless of width option. Providing a distributed AUTO

REFRESH command every 15.625µs will meet the refresh

requirementandensurethateachrowisrefreshed. Alter-

natively, 4,096AUTOREFRESHcommandscanbeissued

The procedure for exiting self refresh requires a se-

quence of commands. First, CLK must be stable (stable

clock is defined as a signal cycling within timing con-

straints specified for the clock pin) prior to CKE going

back HIGH. Once CKE is HIGH, the SDRAM must have

NOP commands issued (a minimum of two clocks) for

t

in a burst at the minimum cycle rate ( RFC), once every

64ms.

t

XSR because time is required for the completion of any

internal refresh in progress.

Upon exiting the self refresh mode, AUTO REFRESH

commands must be issued every 15.625µs or less as both

SELF REFRESH and AUTO REFRESH utilize the row re-

fresh counter.

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

16

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]