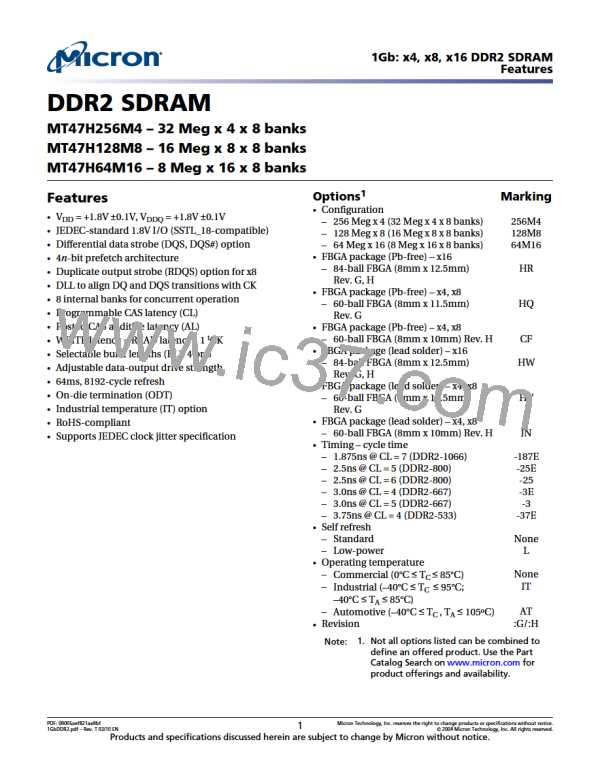

1Gb: x4, x8, x16 DDR2 SDRAM

Figure 51: READ-to-PRECHARGE – BL = 8 ...................................................................................................... 95

Figure 52: Bank Read – Without Auto Precharge ............................................................................................. 97

Figure 53: Bank Read – with Auto Precharge ................................................................................................... 98

Figure 54: x4, x8 Data Output Timing – tDQSQ, tQH, and Data Valid Window .................................................. 99

Figure 55: x16 Data Output Timing – tDQSQ, tQH, and Data Valid Window ..................................................... 100

Figure 56: Data Output Timing – tAC and tDQSCK ......................................................................................... 101

Figure 57: Write Burst ................................................................................................................................... 103

Figure 58: Consecutive WRITE-to-WRITE ...................................................................................................... 104

Figure 59: Nonconsecutive WRITE-to-WRITE ................................................................................................ 104

Figure 60: WRITE Interrupted by WRITE ....................................................................................................... 105

Figure 61: WRITE-to-READ ........................................................................................................................... 106

Figure 62: WRITE-to-PRECHARGE ................................................................................................................ 107

Figure 63: Bank Write – Without Auto Precharge ............................................................................................ 108

Figure 64: Bank Write – with Auto Precharge ................................................................................................. 109

Figure 65: WRITE – DM Operation ................................................................................................................ 110

Figure 66: Data Input Timing ........................................................................................................................ 111

Figure 67: Refresh Mode ............................................................................................................................... 112

Figure 68: Self Refresh .................................................................................................................................. 114

Figure 69: Power-Down ................................................................................................................................ 116

Figure 70: READ-to-Power-Down or Self Refresh Entry .................................................................................. 118

Figure 71: READ with Auto Precharge-to-Power-Down or Self Refresh Entry .................................................. 118

Figure 72: WRITE-to-Power-Down or Self Refresh Entry ................................................................................ 119

Figure 73: WRITE with Auto Precharge-to-Power-Down or Self Refresh Entry ................................................. 119

Figure 74: REFRESH Command-to-Power-Down Entry ................................................................................. 120

Figure 75: ACTIVATE Command-to-Power-Down Entry ................................................................................ 120

Figure 76: PRECHARGE Command-to-Power-Down Entry ............................................................................ 121

Figure 77: LOAD MODE Command-to-Power-Down Entry ............................................................................ 121

Figure 78: Input Clock Frequency Change During Precharge Power-Down Mode ........................................... 122

Figure 79: RESET Function ........................................................................................................................... 124

Figure 80: ODT Timing for Entering and Exiting Power-Down Mode .............................................................. 126

Figure 81: Timing for MRS Command to ODT Update Delay .......................................................................... 127

Figure 82: ODT Timing for Active or Fast-Exit Power-Down Mode ................................................................. 127

Figure 83: ODT Timing for Slow-Exit or Precharge Power-Down Modes ......................................................... 128

Figure 84: ODT Turn-Off Timings When Entering Power-Down Mode ............................................................ 128

Figure 85: ODT Turn-On Timing When Entering Power-Down Mode ............................................................. 129

Figure 86: ODT Turn-Off Timing When Exiting Power-Down Mode ............................................................... 130

Figure 87: ODT Turn-On Timing When Exiting Power-Down Mode ................................................................ 131

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

8

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]