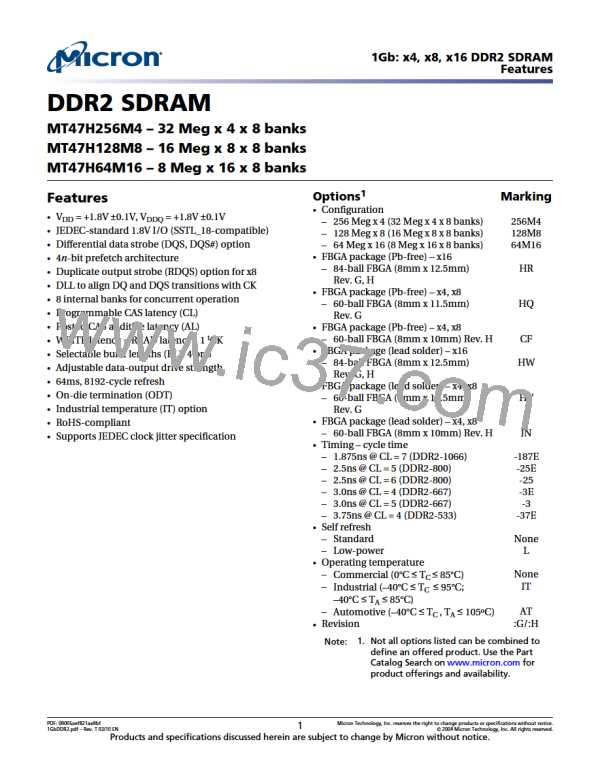

1Gb: x4, x8, x16 DDR2 SDRAM

Functional Block Diagrams

Functional Block Diagrams

The DDR2 SDRAM is a high-speed CMOS, dynamic random access memory. It is inter-

nally configured as a multibank DRAM.

Figure 3: 256 Meg x 4 Functional Block Diagram

ODT

Bank 7

Bank 6

CKE

CK

CK#

Bank 7

Bank 6

Control

logic

Bank 5

Bank 5

Bank 4

Bank 4

Bank 3

Bank 3

Bank 2

Bank 1

CS#

RAS#

CAS#

WE#

Bank 2

ODT control

Vdd Q

CK, CK#

DLL

Bank 1

Bank 0

sw1 sw2 sw3

COL0, COL1

MUX

Bank 0

14

row-

address

latch

4

4

4

4

Memory array

(16,384 x 512 x 16)

Refresh

counter

16,384

14

Mode

registers

sw1 sw2 sw3

Row-

address

MUX

4

16

and

decoder

Read

latch

DRVRS

R1

R1

R2

R2

R3

R3

DATA

17

DQ0–DQ3

DQS, DQS#

DM

14

Sense amplifiers

8,192

2

DQS

generator

DQS, DQS#

16

Input

registers

1

sw1 sw2 sw3

1

1

R1

R1

R2

R2

R3

R3

I/O gating

DM mask logic

1

1

1

4

4

4

4

2

A0–A13,

BA0–BA2

1

4

Address

register

Bank

WRITE

FIFO

and

17

1

control

logic

Mask

3

512

(x16)

1

RCVRS

16

drivers

4

4

4

4

sw1 sw2 sw3

Column

decoder

4

CK out

CK in

16

CK, CK#

R1

R1

R2

R2

R3

R3

Column-

address

counter/

latch

9

Data

11

2

2

COL0, COL1

Vss Q

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

12

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]