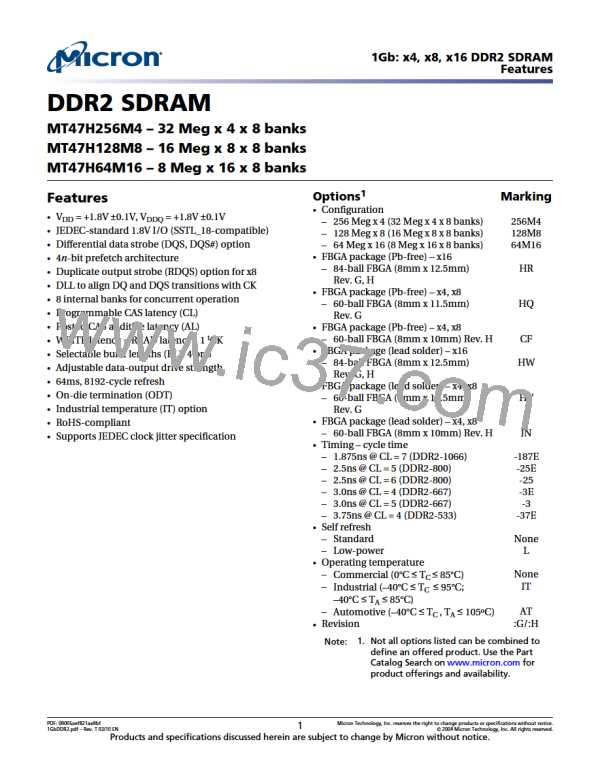

1Gb: x4, x8, x16 DDR2 SDRAM

List of Tables

Table 1: Key Timing Parameters ...................................................................................................................... 2

Table 2: Addressing ......................................................................................................................................... 2

Table 3: FBGA 84-Ball – x16 and 60-Ball – x4, x8 Descriptions .......................................................................... 17

Table 4: Input Capacitance ............................................................................................................................ 22

Table 5: Absolute Maximum DC Ratings ........................................................................................................ 23

Table 6: Temperature Limits .......................................................................................................................... 24

Table 7: Thermal Impedance ......................................................................................................................... 25

Table 8: General IDD Parameters .................................................................................................................... 26

Table 9: IDD7 Timing Patterns (8-Bank Interleave READ Operation) ................................................................. 27

Table 10: DDR2 IDD Specifications and Conditions (Die Revisions E, G, and H) ................................................ 28

Table 11: AC Operating Specifications and Conditions .................................................................................... 31

Table 12: Recommended DC Operating Conditions (SSTL_18) ........................................................................ 41

Table 13: ODT DC Electrical Characteristics ................................................................................................... 42

Table 14: Input DC Logic Levels ..................................................................................................................... 43

Table 15: Input AC Logic Levels ..................................................................................................................... 43

Table 16: Differential Input Logic Levels ........................................................................................................ 44

Table 17: Differential AC Output Parameters .................................................................................................. 46

Table 18: Output DC Current Drive ................................................................................................................ 46

Table 19: Output Characteristics .................................................................................................................... 47

Table 20: Full Strength Pull-Down Current (mA) ............................................................................................ 48

Table 21: Full Strength Pull-Up Current (mA) ................................................................................................. 49

Table 22: Reduced Strength Pull-Down Current (mA) ..................................................................................... 50

Table 23: Reduced Strength Pull-Up Current (mA) .......................................................................................... 51

Table 24: Input Clamp Characteristics ........................................................................................................... 52

Table 25: Address and Control Balls ............................................................................................................... 53

Table 26: Clock, Data, Strobe, and Mask Balls ................................................................................................. 53

Table 27: AC Input Test Conditions ................................................................................................................ 54

Table 28: DDR2-400/533 Setup and Hold Time Derating Values (tIS and tIH) ................................................... 56

Table 29: DDR2-667/800/1066 Setup and Hold Time Derating Values (tIS and tIH) .......................................... 57

Table 30: DDR2-400/533 tDS, tDH Derating Values with Differential Strobe ..................................................... 60

Table 31: DDR2-667/800/1066 tDS, tDH Derating Values with Differential Strobe ............................................ 61

Table 32: Single-Ended DQS Slew Rate Derating Values Using tDSb and tDHb .................................................. 62

Table 33: Single-Ended DQS Slew Rate Fully Derated (DQS, DQ at VREF) at DDR2-667 ..................................... 62

Table 34: Single-Ended DQS Slew Rate Fully Derated (DQS, DQ at VREF) at DDR2-533 ..................................... 63

Table 35: Single-Ended DQS Slew Rate Fully Derated (DQS, DQ at VREF) at DDR2-400 ..................................... 63

Table 36: Truth Table – DDR2 Commands ..................................................................................................... 68

Table 37: Truth Table – Current State Bank n – Command to Bank n ............................................................... 69

Table 38: Truth Table – Current State Bank n – Command to Bank m .............................................................. 71

Table 39: Minimum Delay with Auto Precharge Enabled ................................................................................. 72

Table 40: Burst Definition .............................................................................................................................. 76

Table 41: READ Using Concurrent Auto Precharge ......................................................................................... 96

Table 42: WRITE Using Concurrent Auto Precharge ....................................................................................... 102

Table 43: Truth Table – CKE ......................................................................................................................... 117

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

6

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]