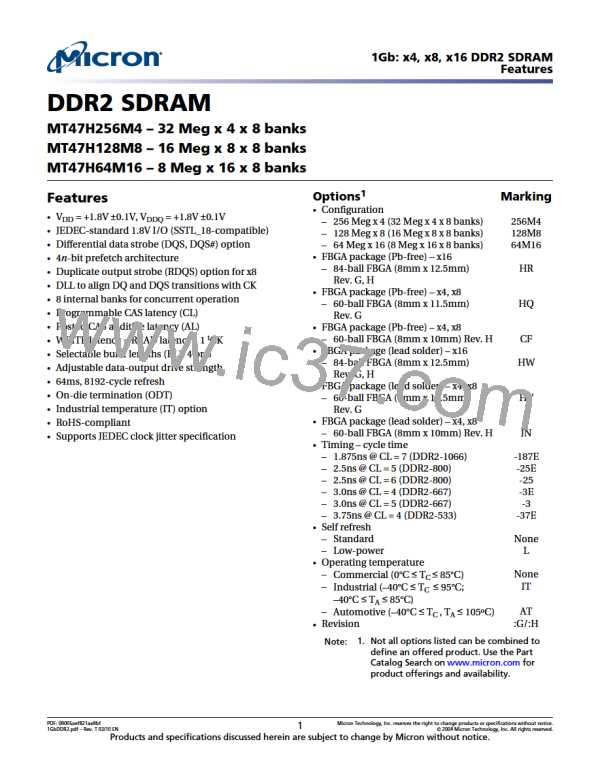

1Gb: x4, x8, x16 DDR2 SDRAM

List of Figures

Figure 1: 1Gb DDR2 Part Numbers ................................................................................................................... 3

Figure 2: Simplified State Diagram ................................................................................................................... 9

Figure 3: 256 Meg x 4 Functional Block Diagram ............................................................................................. 12

Figure 4: 128 Meg x 8 Functional Block Diagram ............................................................................................. 13

Figure 5: 64 Meg x 16 Functional Block Diagram ............................................................................................. 14

Figure 6: 60-Ball FBGA – x4, x8 Ball Assignments (Top View) ........................................................................... 15

Figure 7: 84-Ball FBGA – x16 Ball Assignments (Top View) .............................................................................. 16

Figure 8: 84-Ball FBGA Package (8mm x 12.5mm) – x16 ................................................................................... 19

Figure 9: 60-Ball FBGA Package (8mm x 11.5mm) – x4, x8 ............................................................................... 20

Figure 10: 60-Ball FBGA (8mm x 10mm) – x4, x8 ............................................................................................. 21

Figure 11: Example Temperature Test Point Location ..................................................................................... 24

Figure 12: Single-Ended Input Signal Levels ................................................................................................... 43

Figure 13: Differential Input Signal Levels ...................................................................................................... 44

Figure 14: Differential Output Signal Levels .................................................................................................... 46

Figure 15: Output Slew Rate Load .................................................................................................................. 47

Figure 16: Full Strength Pull-Down Characteristics ......................................................................................... 48

Figure 17: Full Strength Pull-Up Characteristics ............................................................................................. 49

Figure 18: Reduced Strength Pull-Down Characteristics ................................................................................. 50

Figure 19: Reduced Strength Pull-Up Characteristics ...................................................................................... 51

Figure 20: Input Clamp Characteristics .......................................................................................................... 52

Figure 21: Overshoot ..................................................................................................................................... 53

Figure 22: Undershoot .................................................................................................................................. 53

Figure 23: Nominal Slew Rate for tIS .............................................................................................................. 58

Figure 24: Tangent Line for tIS ....................................................................................................................... 58

Figure 25: Nominal Slew Rate for tIH .............................................................................................................. 59

Figure 26: Tangent Line for tIH ...................................................................................................................... 59

Figure 27: Nominal Slew Rate for tDS ............................................................................................................. 64

Figure 28: Tangent Line for tDS ...................................................................................................................... 64

Figure 29: Nominal Slew Rate for tDH ............................................................................................................ 65

Figure 30: Tangent Line for tDH ..................................................................................................................... 65

Figure 31: AC Input Test Signal Waveform Command/Address Balls ............................................................... 66

Figure 32: AC Input Test Signal Waveform for Data with DQS, DQS# (Differential) ........................................... 66

Figure 33: AC Input Test Signal Waveform for Data with DQS (Single-Ended) .................................................. 67

Figure 34: AC Input Test Signal Waveform (Differential) ................................................................................. 67

Figure 35: MR Definition ............................................................................................................................... 75

Figure 36: CL ................................................................................................................................................ 78

Figure 37: EMR Definition ............................................................................................................................. 79

Figure 38: READ Latency ............................................................................................................................... 82

Figure 39: WRITE Latency ............................................................................................................................. 82

Figure 40: EMR2 Definition ........................................................................................................................... 83

Figure 41: EMR3 Definition ........................................................................................................................... 84

Figure 42: DDR2 Power-Up and Initialization ................................................................................................. 85

Figure 43: Example: Meeting tRRD (MIN) and tRCD (MIN) .............................................................................. 88

Figure 44: Multibank Activate Restriction ....................................................................................................... 89

Figure 45: READ Latency ............................................................................................................................... 91

Figure 46: Consecutive READ Bursts .............................................................................................................. 92

Figure 47: Nonconsecutive READ Bursts ........................................................................................................ 93

Figure 48: READ Interrupted by READ ........................................................................................................... 94

Figure 49: READ-to-WRITE ............................................................................................................................ 94

Figure 50: READ-to-PRECHARGE – BL = 4 ...................................................................................................... 95

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

7

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]