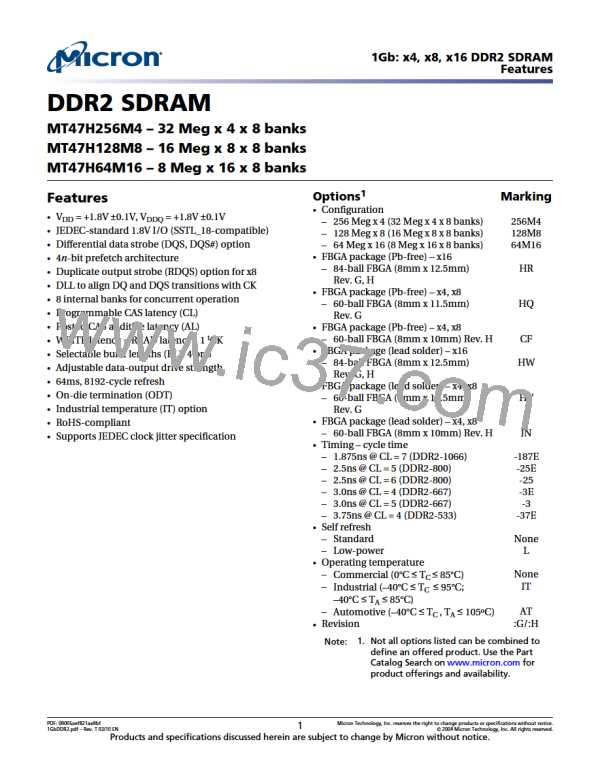

AC Timing Operating Specifications

Table 11: AC Operating Specifications and Conditions

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

VDDQ = +1.8V ±0.1V, VDD = +1.8V ±0.1V

AC Characteristics

Parameter Symbol Min

Clock

cycle time

-187E

-25E

-25

-3E

-3

-37E

-5E

Max Min Max Min Max Min Max Min Max Min Max Min Max Units Notes

CL = 7 tCK (avg) 1.875

CL = 6 tCK (avg) 2.5

CL = 5 tCK (avg) 3.0

CL = 4 tCK (avg) 3.75

8.0

8.0

ns

6, 7, 8,

9

–

–

–

–

–

–

–

–

3.0

3.75

5.0

–

–

–

–

–

–

–

–

–

2.5

2.5

3.75

5.0

8.0

8.0

8.0

8.0

2.5

3.0

3.75

5.0

8.0

8.0

8.0

8.0

–

–

–

8.0

3.0

3.0

5.0

8.0

8.0

8.0

8.0

8.0

8.0

–

–

8.0

–

–

8.0

8.0

3.75

5.0

CL = 3 tCK (avg) 5.0

8.0

5.0

8.0

5.0

8.0

t

CK high-level width CH (avg) 0.48

CK low-level width tCL (avg) 0.48

0.52

0.52

0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 tCK

0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 0.48 0.52 tCK

10

11

Half clock period

tHP

MIN = lesser of tCH and tCL

MAX = n/a

ps

ps

ps

ps

Absolute tCK

tCK (abs)

tCH (abs)

tCL (abs)

MIN = tCK (AVG) MIN + tJITper (MIN)

MAX = tCK (AVG) MAX + tJITper (MAX)

Absolute CK

high-level width

MIN = tCK (AVG) MIN × tCH (AVG) MIN + tJITdty (MIN)

MAX = tCK (AVG) MAX × tCH (AVG) MAX + tJITdty (MAX)

Absolute CK

low-level width

MIN = tCK (AVG) MIN × tCL (AVG) MIN + tJITdty (MIN)

MAX = tCK (AVG) MAX × tCL (AVG) MAX + tJITdty (MAX)

Period jitter

Half period

Cycle to cycle

tJITper

tJITdty

tJITcc

tERR2per –132

tERR3per –157

tERR4per –175

tERR5per –188

–90

–75

90

75

–100 100 –100 100 –125 125 –125 125 –125 125 –125 125

–100 100 –100 100 –125 125 –125 125 –125 125 –150 150

ps

ps

ps

ps

12

13

14

15

180

200

200

250

250

250

250

Cumulative error,

2 cycles

132

157

175

188

250

425

–150 150 –150 150 –175 175 –175 175 –175 175 –175 175

–175 175 –175 175 –225 225 –225 225 –225 225 –225 225

–200 200 –200 200 –250 250 –250 250 –250 250 –250 250

–200 200 –200 200 –250 250 –250 250 –250 250 –250 250

–300 300 –300 300 –350 350 –350 350 –350 350 –350 350

–450 450 –450 450 –450 450 –450 450 –450 450 –450 450

Cumulative error,

3 cycles

ps

ps

ps

ps

ps

15

15

Cumulative error,

4 cycles

Cumulative error,

5 cycles

15, 16

15, 16

15

Cumulative error,

6–10 cycles

tERR6–

10per

tERR11–

50per

–250

–425

Cumulative error,

11–50 cycles

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]