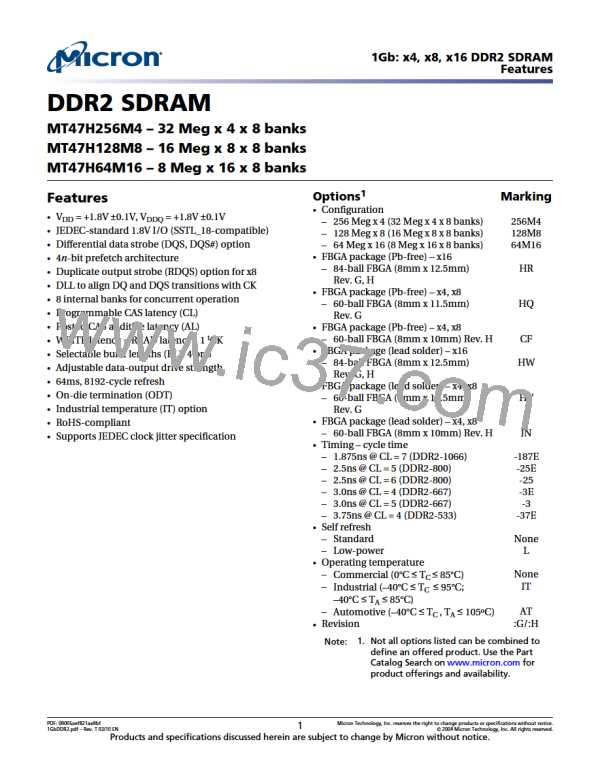

1Gb: x4, x8, x16 DDR2 SDRAM

Electrical Specifications – IDD Parameters

Table 10: DDR2 IDD Specifications and Conditions (Die Revisions E, G, and H)

Notes: 1–7 apply to the entire table

-25E/

-25

-3E/

-3

Parameter/Condition

Symbol Configuration -187E

-37E

70

-5E

70

Units

Operating one bank active-

precharge current:

IDD0

x4, x8

x16

115

180

90

85

mA

150

135

110

110

tCK = tCK (IDD), tRC = tRC (IDD), tRAS

= tRAS MIN (IDD); CKE is HIGH, CS# is

HIGH between valid commands; Ad-

dress bus inputs are switching; Data

bus inputs are switching

Operating one bank active-read-

precharge current: IOUT = 0mA; BL

= 4, CL = CL (IDD), AL = 0; tCK = tCK

(IDD), tRC = tRC (IDD), tRAS = tRAS

MIN (IDD), tRCD = tRCD (IDD); CKE is

HIGH, CS# is HIGH between valid

commands; Address bus inputs are

switching; Data pattern is same as

IDD4W

IDD1

x4, x8

x16

130

210

110

175

100

130

95

90

mA

120

115

Precharge power-down current:

All banks idle; tCK = tCK (IDD); CKE

is LOW; Other control and address

bus inputs are stable; Data bus in-

puts are floating

IDD2P

x4, x8, x16

7

7

7

7

7

mA

mA

Precharge quiet standby

current: All banks idle;

tCK = tCK (IDD); CKE is HIGH, CS# is

HIGH; Other control and address

bus inputs are stable; Data bus in-

puts are floating

IDD2Q

x4, x8

x16

60

90

50

75

40

65

40

45

35

40

Precharge standby current: All

banks idle; tCK = tCK (IDD); CKE is

HIGH, CS# is HIGH; Other control

and address bus inputs are switch-

ing; Data bus inputs are switching

IDD2N

x4, x8

x16

60

95

50

80

40

70

40

50

35

40

mA

mA

mA

Active power-down current: All

banks open; tCK = tCK (IDD); CKE is

LOW; Other control and address

bus inputs are stable; Data bus in-

puts are floating

IDD3Pf

IDD3Ps

Fast exit

MR12 = 0

50

10

40

10

30

10

30

10

30

10

Slow exit

MR12 = 1

Active standby current: All banks

open; tCK = tCK (IDD), tRAS = tRAS

MAX (IDD), tRP = tRP (IDD); CKE is

HIGH, CS# is HIGH between valid

commands; Other control and ad-

dress bus inputs are switching; Data

bus inputs are switching

IDD3N

x4, x8

x16

70

95

60

85

55

75

45

60

40

55

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

28

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]