2 MEG x 16

ASYNC/PAGE/BURST FLASH MEMORY

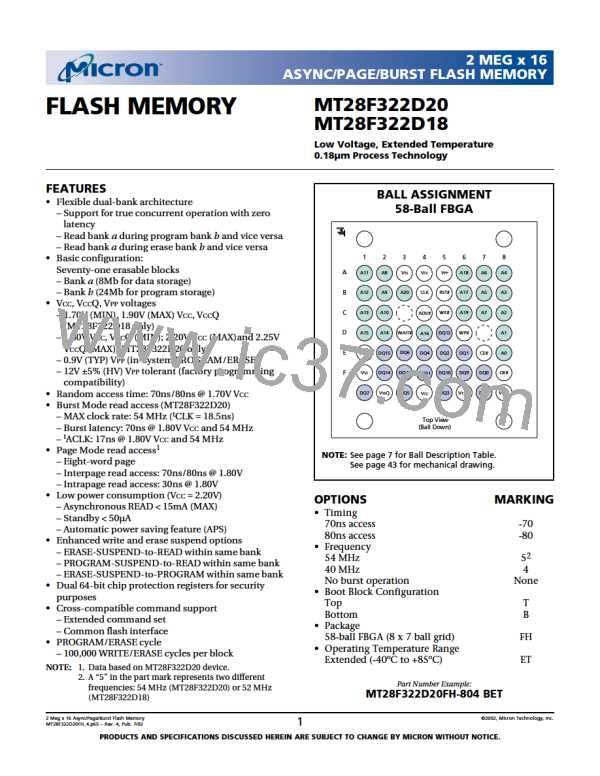

TWO-CYCLE PROGRAMMING/ERASE OPERATION

VIH

VIL

A0–A20

VALID ADDRESS

VALID ADDRESS

t

VALID ADDRESS

t

t

t

AVS

AVH

AS

AH

t

VPH

VIH

VIL

ADV#

CE#

t

t

VP

VS

VIH

VIL

t

t

WOS

CS

t

CH

VIH

VIL

t

WPH

OE#

t

WP

VIH

VIL

VIH

VIL

WE#

t

CMD

WB

CMD/

DATA

CMD/

DATA

High-Z

STATUS

DQ0–DQ15

t

RS

t

DS

t

CH

VIH

t

t

RST#

WP#

RHH

RHS

VIL

VIH

VIL

t

t

VPPH

VPS

VIPPH

VIPPLK

VIL

VPP

UNDEFINED

WRITE TIMING PARAMETERS

-70/-80

-70/-80

SYMBOL

MIN

150

0

MAX

UNITS

ns

SYMBOL

MIN

1.5

3

MAX

UNITS

ns

t

t

t

t

t

t

t

t

t

t

t

RS

AH

t

CS

ns

AVH

WPH

VPH

RHS

VPS

ns

t

WP

70

10

70

70

70

10

0

ns

30

10

0

ns

t

VP

ns

ns

t

DS

ns

ns

t

AS

ns

200

50

0

ns

t

VS

ns

WOS

RHH

VPPH

WB

ns

t

AVS

ns

ns

t

CH

ns

0

ns

t

t

DH

0

ns

AA + 50

ns

2 Meg x 16 Async/Page/Burst Flash Memory

MT28F322D20FH_4.p65 – Rev. 4, Pub. 7/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

39

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]